IP-ядро FFTEx-IP предназначено для выполнения операций БПФ/ОБПФ различной длины над входными данными, представленными в виде квадратурных отсчётов комплексного сигнала.

## Применение

### 1 Базовые станции 3G/4G/LTE/5G NR

Для обработки сигналов и обеспечения высокой производительности и гибкости конфигурации.

### 2 Системы связи с OFDM-модуляцией

Идеально для OFDM-модуляторов и демодуляторов, используемых в различных стандартах беспроводной связи.

### 3 Радиолокационные системы

Для быстрой обработки отражённых сигналов и повышения точности детекции.

### 4 Спутниковая связь и навигация

Для обеспечения высокопроизводительной обработки сигналов в системах GPS и ГЛОНАСС.

## Архитектура

IP-ядро FFTEx-IP реализовано на основе архитектуры Streaming Radix-4. Это архитектура потоковой обработки данных. Она обладает высокой производительностью и предназначена для использования в составе OFDM-модуляторов стандартных (IEEE 802.11n/ac/ax, /LTE/LTE-A/5G NR) и специальных систем связи.

IP-ядро FFTEx-IP можно использовать для демодуляции данных стандарта LTE (TS 36.212) с различным количеством ресурсных блоков: 6, 15, 25, 50, 100, что соответствует частотам дискретизации: 1.92 МГц, 3.84 МГц, 7.68 МГц, 15.36 МГц, 30,72 МГц и полосам пропускания (BW) канала, соответственно, 1.4 МГц, 3 МГц, 5 МГц, 10 МГц, 20 МГц.

## Архитектура Streaming Radix-4

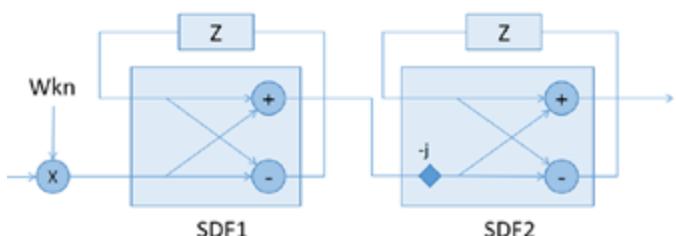

Потоковая архитектура Radix-4 имеет минимальную задержку обработки сигнала. Radix-4 отличается от стандартного решения Radix-2, основанного на перегруппировке и разделении БПФ/ОБПФ. Radix-4 имеет  $\log_4(N)$  стадий, где  $N$  – длина БПФ. Каждая стадия содержит два примитива с задержкой обратной связи (SDF).

На рисунке 1 представлена структура примитива SDF.

Рисунок 1

При необходимости доступно округление и масштабирование на каждой операции типа «бабочка».

IP-ядро FFTEx-IP позволяет изменять тип преобразования с БПФ на ОБПФ и обратно без переконфигурации ядра.

## Сигналы управления и временные диаграммы

Выполнение операций алгоритма начинается после установки сигнала valid\_in в значение логической «1». Полезные выходные данные появляются после установки valid\_out в значение логической «1». Управляющий порт fft\_len определяет размер БПФ/ОБПФ-преобразования для текущего кадра. Предусмотрен порт сброса состояния IP-ядра FFTEx-IP – reset, по сигналу от которого происходит общий сброс всех регистров внутри блока.

При использовании блока в составе OFDM-демодулятора предполагается наличие контроллера входных и выходных данных, который должен формировать данные в соответствии с требуемым количеством ресурсных блоков NRB и частотой дискретизации входных данных.

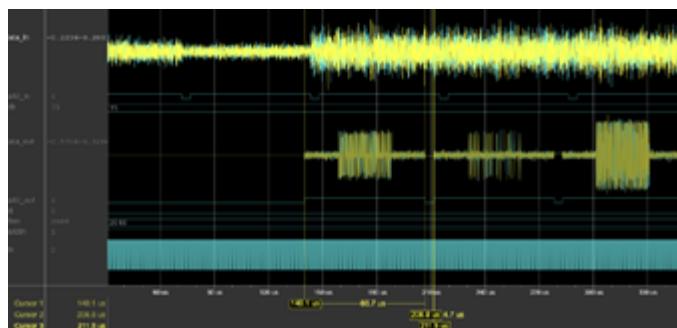

На рис. 2 представлены временные диаграммы сигналов на входе и выходе IP-ядра FFTEx-IP, работающего в составе OFDM-демодулятора с параметрами: fft\_len= 4 (100 ресурсных блоков),  $fs = 30.72$  МГц.

Рисунок 2

На данной временной диаграмме можно увидеть, что длительность выходного валидного OFDM-блока как раз соответствует длительности кадра LTE (TS 36.212) – 66,7 мкс.

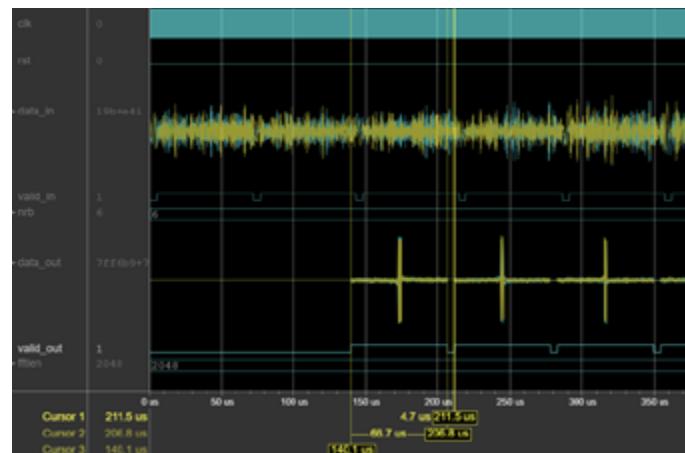

На рис. 3 представлены временные диаграммы сигналов на входе и выходе IP-ядра FFTEx-IP, работающего в составе OFDM-демодулятора с параметрами:  $nrb = 0$  (6 ресурсных блоков),  $fs = 30.72$  МГц.

Рисунок 3

На данной временной диаграмме можно увидеть, что длительность полезных данных уменьшилась и соответствует количеству используемых ресурсных блоков.

## Технические характеристики FFTEx-IP

### Архитектура Streaming Radix-4

- Максимальная тактовая частота работы ядра – 460 МГц (Xilinx Zynq7100/ Zynq7045/ Kintex-7)

- Максимальное значение длины БПФ – 2048

- Минимальное значение длины БПФ – 128

- Поддержка конфигурации количества ресурсных блоков для LTE (TS 36.212) 6, 15, 25, 50, 100

- LUT – 4749

- DSP – 18

- FF – 11831

- RAMB36E1 – 21

## Тестирование и симуляция

Для тестирования и симуляции IP-ядра FFTEx-IP возможна поставка завершённого тестового окружения, реализованного с помощью языков описания Verilog/VHDL с привязкой к конкретному типу симулятора: Mentor Graphics ModelSim/Cadence Incisive/Xilinx Vivado Simulator.

## Интеграция

IP-ядро FFTEx-IP от ЦИТМ Экспонента всегда доступно для целевых платформ FPGA и СБИС. Для специальных применений возможно использование IP-ядра FFTEx-IP в составе специализированных СНК.

Интеграция IP-ядра FFTEx-IP в текущие или будущие проекты возможна в соответствии с требованиями и пожеланиями заказчика. Специалисты ЦИТМ «Экспонента» помогут вам в решении этой задачи.

Свяжитесь с нами, чтобы узнать

больше технических подробностей!

+7 (495) 009 65 85

[info@exponenta.ru](mailto:info@exponenta.ru)

[www.exponenta.ru](http://www.exponenta.ru)