# КАТАЛОГ

## Программные IP-блоки

## Цифровые предыскажения сигнала

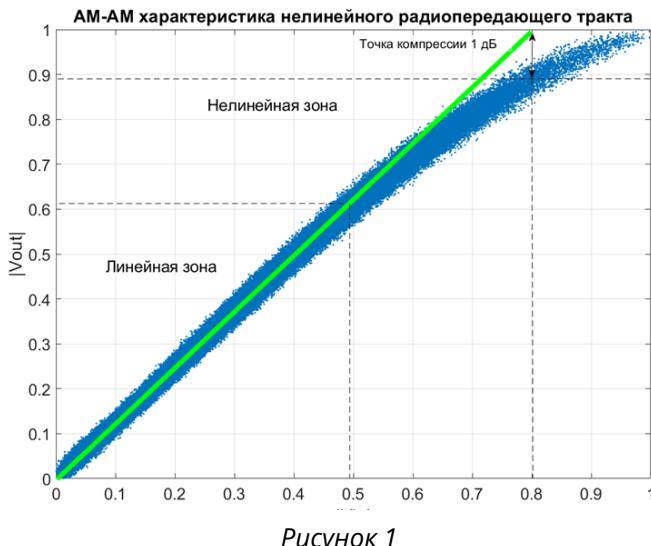

Современные и проектируемые системы радиосвязи (3G/4G/5G, LTE/LTE-A, Wi-Fi 802.11n/ac/ax), предназначенные для передачи больших объёмов информации, предполагают использование каналов с высокой спектральной эффективностью (бит/(с×Гц)). В свою очередь, высокая спектральная эффективность, как правило, приводит к высокому уровню пик-фактора формируемого сигнала ( $\text{PAPR} > 3 \text{ dB}$ ). Всё это накладывает жёсткие требования к линейности радиопередающего тракта (ACPR, ACLR, EVM), что приводит к увеличению стоимости, габаритов и одновременно к снижению КПД всей системы радиосвязи. На рисунке 1 представлена типовая нелинейная передаточная характеристика (AM-AM).

Для решения проблемы линейности радиопередающего тракта и одновременно сохранения энергетических характеристик системы радиосвязи оптимальным является использование цифровых предыскажений формируемого сигнала (DPD).

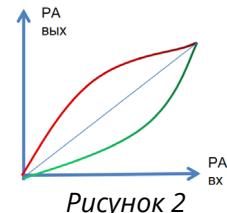

На рисунке 2 представлен принцип действия DPD применительно к нелинейной передаточной характеристике (AM-AM).

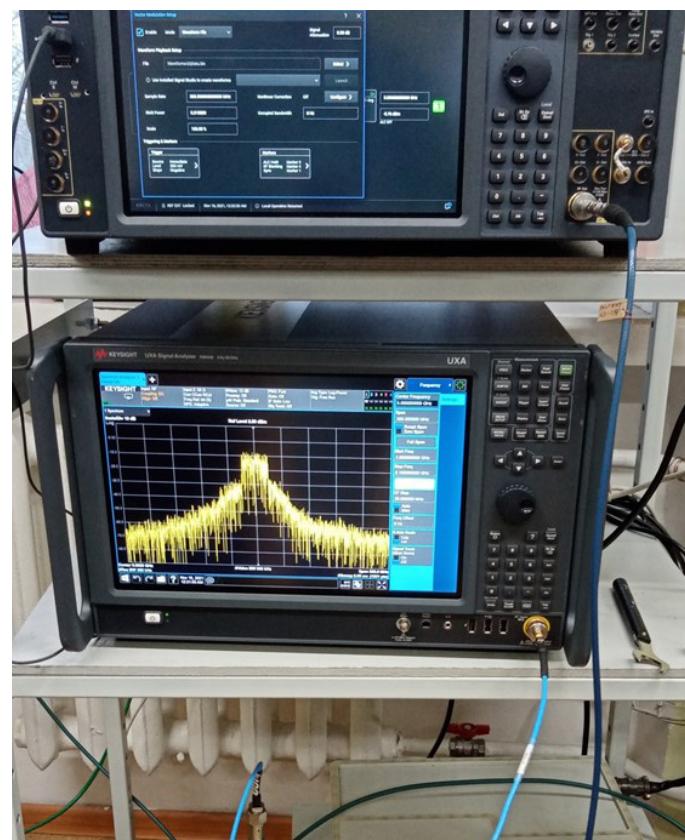

В течение последних нескольких лет компания ЦИТМ «Экспонента» ведёт исследование и разработку систем ввода цифровых предыскажений DPD. На рисунке 3 представлен стенд измерения и отладки алгоритмов ЦОС для разработки систем связи с использованием DPD.

Разработка алгоритмов DPD довольно сложная задача, требующая большого количества времени и ресурсов, при этом конечный результат может потребовать значительных вычислительных ресурсов от целевой платформы.

Для снижения потенциальных затрат и потерь разработчиков систем связи компания ЦИТМ «Экспонента» предлагает

IP-ядро собственной разработки DPDex-IP, предназначенное для линеаризации радиопередающего тракта современных систем радиосвязи.

## Описание

IP-ядро DPDex-IP предназначено для непосредственного ввода цифровых предыскажений в формируемый сигнал. Архитектура IP-ядра DPDex-IP не привязана к конкретному производителю ПЛИС/СБИС, что повышает гибкость и независимость, разрабатываемых систем радиосвязи.

Предыскажение входного сигнала осуществляется в соответствии с загружаемыми коэффициентами. Загрузка коэффициентов возможна через базовый «нативный» порт, а также через стандартный интерфейс AXI4-Lite. Таким образом, IP-ядро DPDex-IP способно работать с системами адаптации, действующими в режиме постоянного обновления коэффициентов (расчёт ведётся на ПЛИС/СБИС) и с системами адаптации, предусматривающими периодическое обновление коэффициентов с помощью soft-процессора, например, ARM/Nios/Microblaze/RISC-V. IP-ядро DPDex-IP имеет встроенную цепь обхода DPD, т.е. позволяет оперативно включать и выключать ввод предыскажений.

Дополнительно IP-ядро DPDex-IP осуществляет вычисление модуля сигнала для прямого и обратного каналов, что позволяет контролировать уровень сигнала на выходе радиопередающего тракта. Кроме того, дополнительно IP-ядро DPDex-IP может применять заранее рассчитанные коэффициенты, что удобно для тех систем, где нелинейные свойства радиопередающего тракта не изменяются со временем. Для масштабирования и задания необходимого уровня сигнала может использоваться входной 18-битный умножитель.

## Технические характеристики

- Архитектура – Memory Polynomial Advanced

- Максимальная полоса предыскажаемого сигнала – 220 МГц

- Максимальная тактовая частота работы ядра – 450 МГц (Xilinx Zynq7100/ Zynq7045)

- Максимальное кол-во коэффициентов – 21

### Ресурсы (P=5, M=5):

- LUT – 4682

- DSP – 57 (в режиме 1 clk/sample)/ 31 (в режиме 2 clk/sample) при максимальном количестве коэффициентов

- FF – 12645 (в режиме 1 clk/sample при максимальной тактовой частоте 450 МГц)

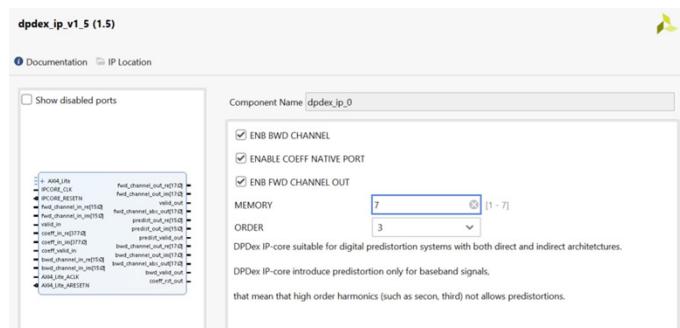

Рисунок 4

## Производительность

IP-ядро DPDex-IP реализовано с учётом максимальных требований к быстродействию и производительности.

ЦИТМ «Экспонента» предлагает улучшенную реализацию архитектуры ввода цифровых предыскажений – Memory Polynomial Advanced. Улучшения архитектуры коснулись быстродействия, точности вычислений, минимизации вычислительных ресурсов.

Основным преимуществом IP-ядра DPDex-IP является возможность предыскажения сверхширокополосных сигналов (до 220 МГц).

Степень подавления уровня помехи в соседнем канале (ACLR/ACPR) зависит от качества рассчитанных коэффициентов предыскажения, нелинейных свойств усилителя мощности, полосы предыскажаемого сигнала. Качество коэффициентов предыскажения определяется алгоритмами расчёта/адаптации. Наилучших результатов позволяют добиться алгоритмы на основе RLS-методов.

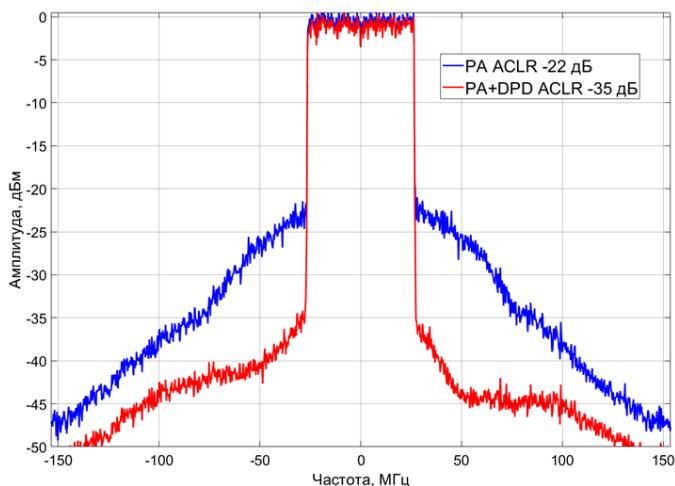

Типовое значение подавления ACLR/ACPR лежит в диапазоне от 10 дБ до 25 дБ. На рисунке 5 представлен спектр сигнала без предыскажений и с использованием предыскажений DPDex-IP.

Рисунок 5

С практической точки зрения наиболее важным является анализ такого параметра, как EVM (error vector magnitude) – модуля вектора ошибки.

Свяжитесь с нами, чтобы узнать больше технических подробностей!

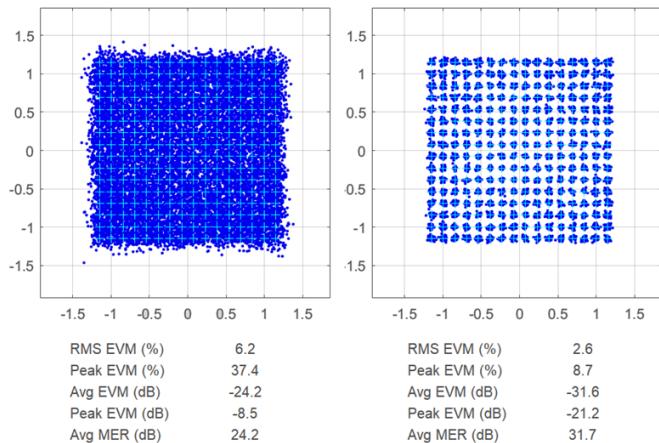

На рисунке 6 представлены созвездия сигналов формата QAM-256 без предыскажений и с использованием предыскажений DPDex-IP.

Рисунок 6

Очевидно, что использование IP-ядра DPDex-IP приводит к существенному существенному повышению качества сигнала. EVM сигнала улучшен на 3,6 % (более, чем в два раза).

## Интеграция

IP-ядро DPDex-IP ЦИТМ «Экспонента» всегда доступно для целевых платформ FPGA и СБИС. Для специальных применений возможно использование IP-ядра DPDex-IP в составе специализированных СнК.

Интеграция IP-ядра DPDex-IP в текущие или будущие проекты возможна в соответствии с любыми требованиями и пожеланиями заказчика. Специалисты ЦИТМ «Экспонента» помогут вам в решении этой задачи.

IP-ядро FFTEx-IP предназначено для выполнения операций БПФ/ОБПФ различной длины над входными данными, представленными в виде квадратурных отсчётов комплексного сигнала.

## Применение

### 1 Базовые станции 3G/4G/LTE/5G NR

Для обработки сигналов и обеспечения высокой производительности и гибкости конфигурации.

### 2 Системы связи с OFDM-модуляцией

Идеально для OFDM-модуляторов и демодуляторов, используемых в различных стандартах беспроводной связи.

### 3 Радиолокационные системы

Для быстрой обработки отражённых сигналов и повышения точности детекции.

### 4 Спутниковая связь и навигация

Для обеспечения высокопроизводительной обработки сигналов в системах GPS и ГЛОНАСС.

## Архитектура

IP-ядро FFTEx-IP реализовано на основе архитектуры Streaming Radix-4. Это архитектура потоковой обработки данных. Она обладает высокой производительностью и предназначена для использования в составе OFDM-модуляторов стандартных (IEEE 802.11n/ac/ax, /LTE/LTE-A/5G NR) и специальных систем связи.

IP-ядро FFTEx-IP можно использовать для демодуляции данных стандарта LTE (TS 36.212) с различным количеством ресурсных блоков: 6, 15, 25, 50, 100, что соответствует частотам дискретизации: 1.92 МГц, 3.84 МГц, 7.68 МГц, 15.36 МГц, 30,72 МГц и полосам пропускания (BW) канала, соответственно, 1.4 МГц, 3 МГц, 5 МГц, 10 МГц, 20 МГц.

## Архитектура Streaming Radix-4

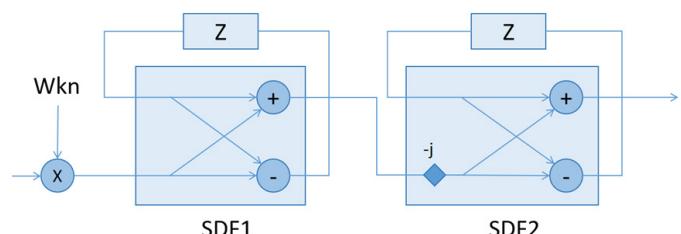

Потоковая архитектура Radix-4 имеет минимальную задержку обработки сигнала. Radix-4 отличается от стандартного решения Radix-2, основанного на перегруппировке и разделении БПФ/ОБПФ. Radix-4 имеет  $\log_4(N)$  стадий, где N – длина БПФ. Каждая стадия содержит два примитива с задержкой обратной связи (SDF).

На рисунке 1 представлена структура примитива SDF.

Рисунок 1

При необходимости доступно округление и масштабирование на каждой операции типа «бабочка».

IP-ядро FFTEx-IP позволяет изменять тип преобразования с БПФ на ОБПФ и обратно без переконфигурации ядра.

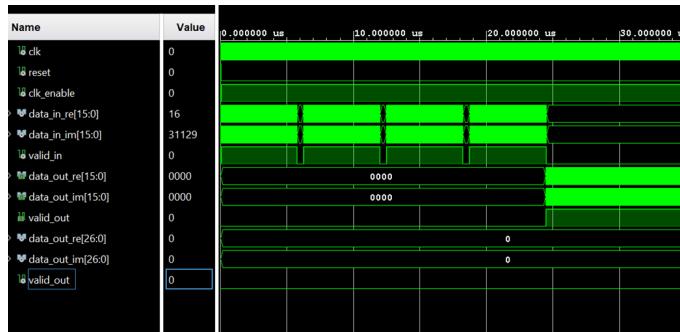

## Сигналы управления и временные диаграммы

Выполнение операций алгоритма начинается после установки сигнала valid\_in в значение логической «1». Полезные выходные данные появляются после установки valid\_out в значение логической «1». Управляющий порт fft\_len определяет размер БПФ/ОБПФ-преобразования для текущего кадра. Предусмотрен порт сброса состояния IP-ядра FFTEx-IP – reset, по сигналу от которого происходит общий сброс всех регистров внутри блока.

При использовании блока в составе OFDM-демодулятора предполагается наличие контроллера входных и выходных данных, который должен формировать данные в соответствии с требуемым количеством ресурсных блоков NRB и частотой дискретизации входных данных.

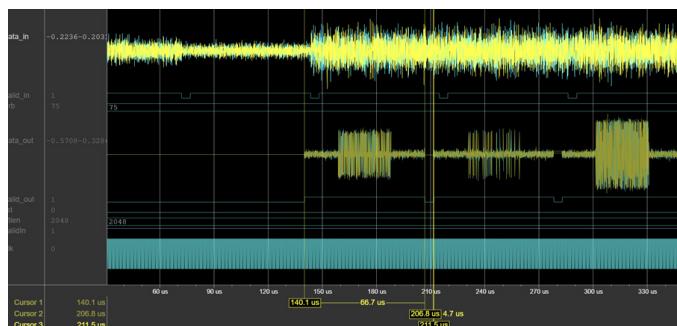

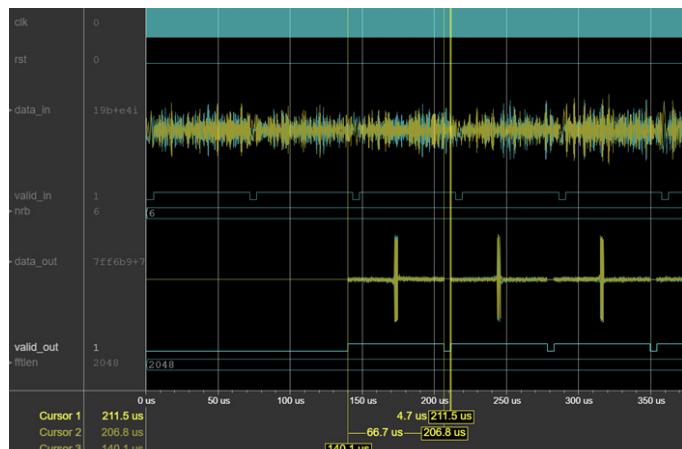

На рис. 2 представлены временные диаграммы сигналов на входе и выходе IP-ядра FFTEx-IP, работающего в составе OFDM-демодулятора с параметрами: fft\_len= 4 (100 ресурсных блоков), fs = 30.72 МГц.

Рисунок 2

На данной временной диаграмме можно увидеть, что длительность выходного валидного OFDM-блока как раз соответствует длительности кадра LTE (TS 36.212) – 66,7 мкс.

На рис. 3 представлены временные диаграммы сигналов на входе и выходе IP-ядра FFTEx-IP, работающего в составе OFDM-демодулятора с параметрами: nrb = 0 (6 ресурсных блоков), fs = 30.72 МГц.

Рисунок 3

На данной временной диаграмме можно увидеть, что длительность полезных данных уменьшилась и соответствует количеству используемых ресурсных блоков.

## Технические характеристики FFTEx-IP

### Архитектура Streaming Radix-4

- Максимальная тактовая частота работы ядра – 460 МГц (Xilinx Zynq7100/ Zynq7045/ Kintex-7)

- Максимальное значение длины БПФ – 2048

- Минимальное значение длины БПФ – 128

- Поддержка конфигурации количества ресурсных блоков для LTE (TS 36.212) 6, 15, 25, 50, 100

- LUT – 4749

- DSP – 18

- FF – 11831

- RAMB36E1 – 21

## Тестирование и симуляция

Для тестирования и симуляции IP-ядра FFTEx-IP возможна поставка завершённого тестового окружения, реализованного с помощью языков описания Verilog/VHDL с привязкой к конкретному типу симулятора: Mentor Graphics ModelSim/Cadence Incisive/Xilinx Vivado Simulator.

## Интеграция

IP-ядро FFTEx-IP от ЦИТМ Экспонента всегда доступно для целевых платформ FPGA и СБИС. Для специальных применений возможно использование IP-ядра FFTEx-IP в составе специализированных СНК.

Интеграция IP-ядра FFTEx-IP в текущие или будущие проекты возможна в соответствии с требованиями и пожеланиями заказчика. Специалисты ЦИТМ «Экспонента» помогут вам в решении этой задачи.

## Снижение пик-фактора сигнала

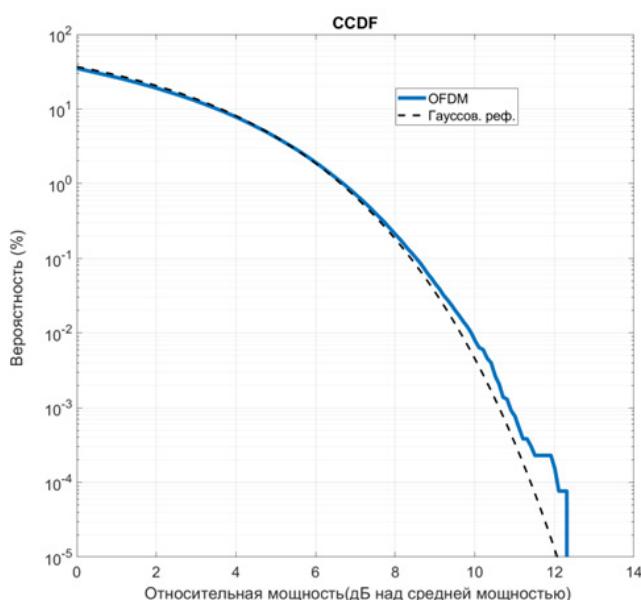

Современные стандарты радиосвязи 4G(LTE/LTE-A)/5G используют OFDM-сигналы, что даёт им высокую спектральную эффективность. Однако у такого вида сигналов очень высокий уровень пик-фактора (PAPR>10 дБ), т.е. отношение пиковой мощности сигнала к средней мощности сигнала. На рисунке 1 представлена комплементарная кумулятивная функция распределения вероятностей для OFDM-сигнала с количеством поднесущих, равным 2048, и модуляцией 256-QAM.

Высокий уровень пик-фактора приводит к снижению КПД усилителей мощности на выходе радиопередающих устройств, так как большую часть времени излучается сигнал сравнительно небольшой мощности. Кроме того, существенно снижается эффективность систем ввода цифровых предыскажений (DPD) для сигналов с высоким пик-фактором, так как основную часть времени сигнал находится в линейной зоне работы усилителя мощности.

Рисунок 1

Всё это приводит к тому, что для эффективной передачи сигналов стандартов 4G(LTE/LTE-A)/5G требуются усилители высокой мощности и линейности, что приводит к удорожанию оборудования, увеличению массы и габаритов систем связи.

Для решения проблем систем радиосвязи, связанных с высоким уровнем пик-фактора сигнала, компания ЦИТМ «Экспонента» разработала технологии и методы снижения пик-фактора сигнала, применимые для современных стандартов связи, включая 4G(LTE/LTE-A)/5G технологии. Основная идея в снижении пик-фактора – это уменьшение пиковой мощности сигнала. В разное время были представлены различные методы снижения пик-фактора: оконные функции (peak windowing), жёсткое клипирование (hard clipping), сигналозависимые алгоритмы (tone reservation, active constellation extension). Одним из наиболее прогрессивных методов стал Peak cancellation crest factor reduction (PC-CFR). Данный метод имеет один из лучших показателей по снижению пик-фактора, при этом он использует существенно меньшие вычислительные ресурсы в сравнении с другими методами.

Уже несколько лет компания ЦИТМ «Экспонента» ведёт исследование и разработку систем снижения пик-фактора, основанных на прогрессивном методе PC-CFR. И теперь мы готовы представить IP-ядро собственной разработки PC-CFReX-IP, предназначенное для снижения пик-фактора сигнала стандартных (4G(LTE/LTE-A)/5G и др.) и нестандартных систем связи (custom OFDM). Уникальность данного IP-ядра в том, что его архитектура не привязана к какому-либо стандарту и является гибкой и конфигурируемой в режиме «онлайн», не требуя переконфигурации проектов.

## Описание PC-CFReX-IP

IP-ядро PC-CFReX-IP предназначено для снижения пик-фактора сигнала. Архитектура IP-ядра PC-CFReX-IP не привязана к конкретному производителю ПЛИС/СБИС, что повышает гибкость и независимость разрабатываемых систем радиосвязи. IP-ядро PC-CFReX-IP (ЦИТМ «Экспонента») и IP-ядро DP Dex-IP (ЦИТМ «Экспонента») полностью совместимы и составляют готовое DFE-решение (Digital Front-End) для современных систем связи.

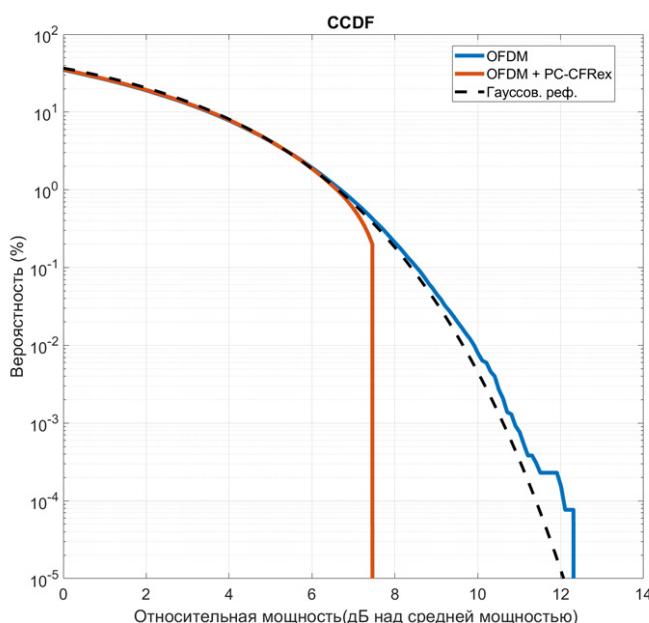

На рисунке 2 представлена комплементарная кумулятивная функция распределения вероятностей для OFDM-сигнала и для OFDM-сигнала с использованием IP-ядра PC-CFReX-IP.

Рисунок 2

Как видно из графика, эффективное снижение пик-фактора при использовании IP-ядра PC-CFReX-IP более чем на 4.0 дБ ( $\text{PAPR}=7.7 \text{ дБ}/\text{EVM}_{\text{rms}} = 3.0\%$ ).

Снижение пик-фактора осуществляется за счёт использования специальных коэффициентов импульсных характеристик – peak cancellations. Коэффициенты загружаются через стандартный интерфейс AXI-4Lite. Максимальная скорость загрузки ограничена только производительностью интерфейса AXI-4Lite. Для расчёта коэффициентов используется специализированное ПО, поставляемое вместе с IP-ядром PC-CFReX-IP.

IP-ядро PC-CFReX-IP спроектировано таким образом, что позволяет снижать пик-фактор сигнала, при этом не допуская существенного расширения спектра сигнала. Это достигается за счёт методики расчёта коэффициентов импульсных характеристик (peak cancellations) и многокаскадной архитектуры, которая итеративно снижает пик-фактор сигнала.

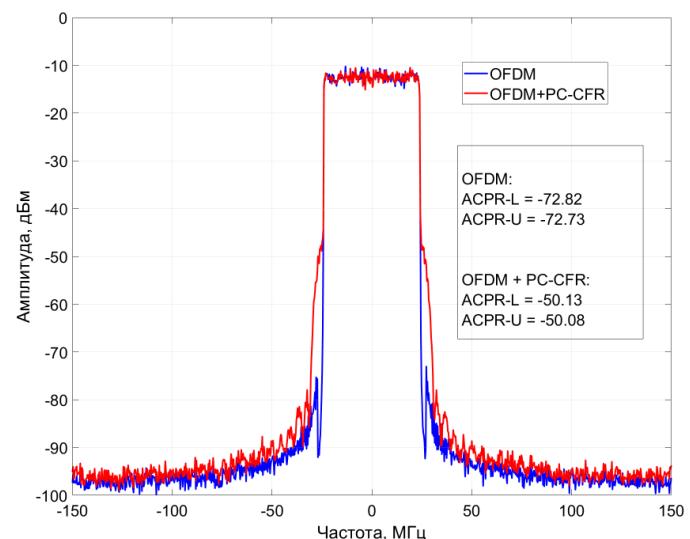

На рисунке 3 представлены спектры OFDM-сигнала шириной полосы частот 50 МГц с использованием и без использования IP-ядра PC-CFReX-IP.

Рисунок 3

Другим немаловажным показателем эффективности работы IP-ядра PC-CFReX-IP является низкий уровень вносимых искажений.

Значение EVM<sub>rms</sub> при использовании PC-CFReX-IP для OFDM с модуляциями 256-QAM/64-QAM находится в пределах 3.2% при эффективном PAPR=7.7 дБ.

В таблице 1 представлено сравнение с аналогичными решениями от других производителей. Информация взята из открытых источников.

Таблица 1

| Производитель  | Lattice Semi   | Altera         | Xilinx         | Texas Instr    | Systems 4Silicon | ЦИТМ Экспонента   |

|----------------|----------------|----------------|----------------|----------------|------------------|-------------------|

| Тип сигнала    | LTE 20 MHz       | <b>LTE 20 MHz</b> |

| PAPR w/CFR, дБ | 7.3            | 6.5            | 7.5            | 8              | 7                | <b>7.6</b>        |

| EVM, %         | 3.7            | 13.8           | 4              | -              | 5                | <b>3.2</b>        |

| Тип CFR        | non-data-aided | non-data-aided | non-data-aided | non-data-aided | non-data-aided   | non-data-aided    |

Также IP-ядро PC-CFReX-IP содержит встроенный аппаратный «hard clipper», который позволяет осуществлять сжатие динамического диапазона без учёта расширения спектра.

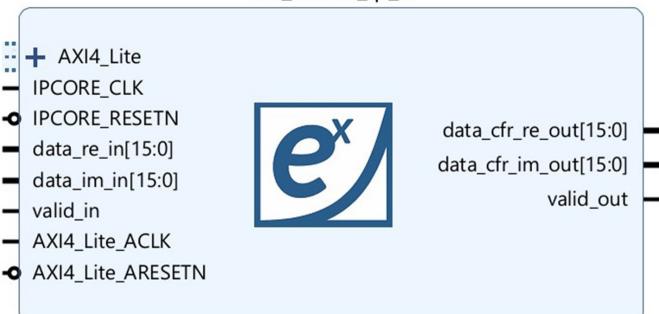

PC\_CFRex\_ip\_0

PC\_CFRex\_ip

Рисунок 4

Свяжитесь с нами, чтобы узнать больше технических подробностей!

## Технические характеристики

- Архитектура – Non data aided (Peak cancellation+Hard clipper)

- Максимальная эффективная полоса входного сигнала – 80 МГц (при максимальной тактовой частоте 400 МГц)

- Максимальная тактовая частота работы ядра – 400 МГц (Xilinx Zynq7100/ Zynq7045/ Kintex-7)

- Максимальное кол-во стадий обработки – 3

- LUT – 11300

- DSP – 30

- FF – 16213 (в режиме 1 clk/sample при максимальной тактовой частоте 400 МГц)

- Встроенный «hard clipper»

- Управление IP-ядром по AXI4-Lite

- Онлайн-загрузка коэффициентов импульсных характеристик по AXI4-Lite и импульсных характеристик по AXI4-Lite

## Интеграция

IP-ядро PC-CFReX-IP ЦИТМ «Экспонента» всегда доступно для целевых платформ FPGA и СБИС. Для специальных применений возможно использование IP-ядра PC-CFReX-IP в составе специализированных СНК. Специалисты ЦИТМ «Экспонента» помогут интегрировать IP-ядро PC-CFReX-IP в текущие или будущие проекты и учат любые требования и пожелания заказчика.

+7 (495) 009 65 85

info@exponenta.ru

www.exponenta.ru

IP-ядро OFDMex-IP предназначено для работы в качестве OFDM-модулятора или OFDM-демодулятора в трактах цифровой обработки сигналов различных систем связи. Данная версия IP-ядра имеет повышенное быстродействие благодаря использованию новой реализации высокопроизводительного потокового алгоритма FFT.

## Применение

### 1 Системы связи с OFDM-модуляцией

IP-ядро идеально подходит для приемопередающих устройств, использующих технологию OFDM в сочетании с различными стандартами связи.

### 2 Оборудование для систем цифрового телевидения DVB

### 3 Системы беспроводного доступа Wi-Fi (IEEE 802.11a/n/ac/ax/be)

### 4 Базовые станции 4G/LTE/5G NR

IP-ядро используется для обработки сигналов в базовых станциях мобильной связи, обеспечивая высокую производительность и гибкость конфигурации.

## Архитектура

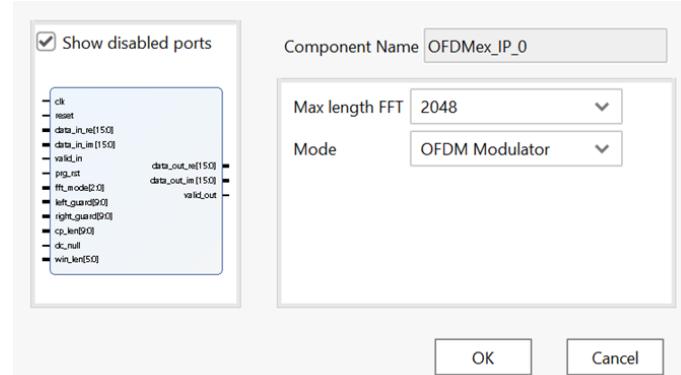

IP-ядро OFDMex-IP предоставляет пользователю возможность конфигурации с целью выбора режима работы и максимальной длины FFT. Последнее позволяет в случае необходимости оптимизировать используемые ресурсы FPGA. При конфигурации доступен выбор режима работы OFDM-модулятор или OFDM-демодулятор. Максимальная длина FFT может быть установлена из ряда: 64, 128, 256, 512, 1024, 2048.

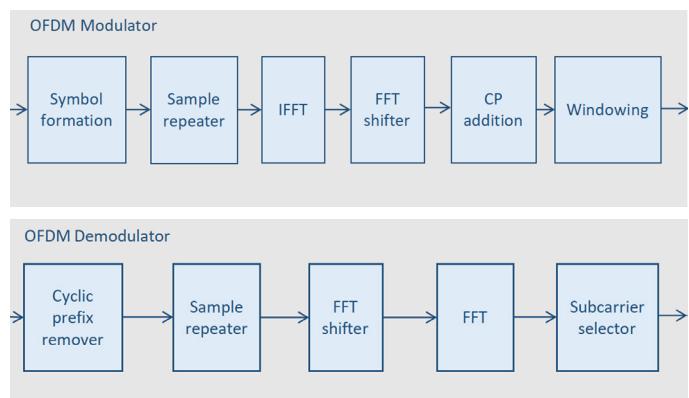

На рисунке 1 показаны структурные схемы ядра в режиме модулятора и демодулятора. При работе в режиме модулятора IP-ядро принимает на вход комплексные отсчёты, формирующие спектр OFDM-символа. Полный спектр формируется с помощью формирователя OFDM-символа (Symbol formation) с учётом требуемого размера защитных интервалов. Далее с помощью повторителя (Sample repeater) в случае, если длина FFT меньше максимальной длины, формируется полный набор отсчётов для обратного преобразования Фурье (IFFT). Поскольку входные данные модулятора представлены как симметричный спектр, спектр сигнала на выходе IFFT смещается на половину частоты дискретизации.

После этого к OFDM-символу во временной области добавляется циклический префикс требуемой длины. В случае использования оконной обработки в конце также добавляется суффикс с длиной, равной длине окна. Кроме того, в начале префикса и для суффикса применяется умножение на оконную функцию (Windowing). В выходной последовательности префикс перекрывается с суффиксом предыдущего символа.

Рисунок 1

При работе в режиме демодулятора IP-ядро принимает на входе OFDM-символы во временной области. При этом сначала происходит удаление циклического префикса.

Далее, если длина символа меньше максимального размера FFT, с помощью периодического повторения формируется последовательность длины, необходимой для FFT. Так как отсчеты на выходе демодулятора интерпретируются как симметричный спектр, перед FFT во временной области спектр сигнала смещается на половину частоты дискретизации. После выполнения преобразования Фурье из спектра выделяются необходимые компоненты и подаются на выход.

## Сигналы управления и временные диаграммы

Обработка поступающих на входные порты данных начинается после установки сигнала `valid_in` в значение логической «1». Полезные выходные данные появляются после установки `valid_out` в значение логической «1». Управляющий порт `fft_mode` определяет размер FFT/IFFT преобразования для текущего OFDM-символа. Номер режима выбирается из ряда: 0, 1, 2, 3, 4, 5, что соответствует длине FFT 64, 128, 256, 512, 1024, 2048 соответственно. С помощью портов `cp_len`, `left_guard`, `right_guard` задаются соответственно длина циклического префикса, размер левого и правого защитного интервала. Порт `dc_null` в режиме модулятора используется для установки режима автоматической вставки отсчета нулевой постоянной составляющей. В режиме демодулятора порт `dc_null` используется для установки режима удаления отсчета постоянной составляющей из выходных данных. В режиме модулятора существует дополнительный порт `win_len` для установки длины окна при оконной обработке. Максимальная длина окна – `win_len = 32` отсчета. При установке длины `win_len = 0` оконная обработка не выполняется. Также предусмотрен порт сброса состояния IP-ядра OFDMex-IP – `prg_RST`, по сигналу от которого происходит общий сброс всех регистров внутри блока.

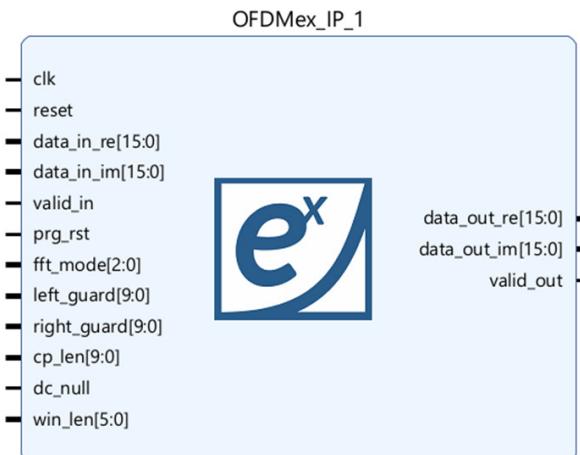

На рисунке 2 показан пример дизайна системы с использованием IP-ядер OFDMex-IP. При конфигурации ядер пользователю необходимо указать режим работы ядра и максимальную длину FFT (рисунок 3).

OFDMex\_IP\_v1\_1

Рисунок 2

Рисунок 3

Обработка данных в ядре OFDMex-IP имеет высокую степень конвейеризации. Задержка данных между входом и выходом зависит от конфигурации и значений текущих параметров. Запуск цикла обработки OFDM-символа происходит после того, как на вход ядра поступят все данные, необходимые для формирования или демодуляции.

На рисунке 4 показан пример временных диаграмм работы модулятора. На вход модулятора непрерывно поступают данные для формирования четырех OFDM-символов. Как видно, данные на выходе появляются с задержкой, обусловленной конвейерной обработкой.

Рисунок 4

Аналогичным образом выглядят временные диаграммы работы в режиме демодулятора (рисунок 5).

Рисунок 5

## Совместимость со стандартом LTE

IP-ядро OFDMex-IP может быть использовано в системах связи стандарта LTE с количеством ресурсных блоков (NDLRB): 6, 15, 25, 50, 100. Для этого необходимо сконфигурировать ядро на максимальную длину FFT 2048 и обеспечить подачу на входные порты соответствующих параметров исходя из стандарта. Например, для NDLRB = 50 в режиме extended CP следует установить параметры: fft\_mode = 4, dc\_null = 1, cp\_len = 256, left\_guard = 212, right\_guard = 211.

## Технические характеристики

- Режимы работы:

- OFDM-модулятор

- OFDM-демодулятор

- Максимальное значение длины FFT, устанавливаемое при конфигурации – 64, 128, 256, 512, 1024, 2048

- Значение длины FFT, устанавливаемое через порт – 64, 128, 256, 512, 1024, 2048 (`fft_len <= FFTmax`)

- Максимальная длина окна при оконной обработке в модуляторе – 32 (по стандарту IEEE 802.11g)

Следующие параметры IP-ядра зависят от конкретной конфигурации. Для справки приведены некоторые значения.

### Модулятор, FFTmax = 64

- Максимальная тактовая частота работы ядра – 405 МГц (Xilinx Zynq7100-2)

- LUT – 3074

- DSP – 10

- FF – 7124

- RAMB36E1 – 1.5

### Модулятор, FFTmax = 2048

- Максимальная тактовая частота работы ядра – 405 МГц (Xilinx Zynq7100-2)

- LUT – 4684

- DSP – 19

- FF – 11526

- RAMB36E1 – 19

### Демодулятор, FFTmax = 64

- Максимальная тактовая частота работы ядра – 410 МГц (Xilinx Zynq7100-2)

- LUT – 3119

- DSP – 6

- FF – 6542

- RAMB36E1 – 0.5

### Демодулятор, FFTmax = 2048

- Максимальная тактовая частота работы ядра – 409 МГц (Xilinx Zynq7100-2)

- LUT – 5860

- DSP – 18

- FF – 12689

- RAMB36E1 – 19

## Тестирование и симуляция

Для тестирования и симуляции IP-ядра OFDMex-IP возможна поставка завершенного тестового окружения, реализованного с помощью языков описания Verilog/VHDL с привязкой к конкретному типу симулятора: Mentor Graphics ModelSim/Cadence Incisive/Xilinx Vivado Simulator.

## Интеграция

IP-ядро OFDMex-IP ЦИТМ «Экспонента» всегда доступно для целевых платформ FPGA и СБИС. При наличии специфических требований возможно рассмотрение доработки ядра. Для специальных применений возможно использование IP-ядра OFDMex-IP в составе специализированных СНК.

Специалисты ЦИТМ «Экспонента» помогут интегрировать IP-ядро OFDMex-IP в текущие или будущие проекты и учтут любые требования и пожелания заказчика.

Свяжитесь с нами, чтобы узнать

больше технических подробностей!

+7 (495) 009 65 85

[info@exponenta.ru](mailto:info@exponenta.ru)

[www.exponenta.ru](http://www.exponenta.ru)

## Сверточное декодирование Витерби

В современных системах связи существует необходимость передачи данных и их восстановления без ошибок даже при наличии помех. В случае возникновения ошибок требуется избежать повторной передачи данных, чтобы не допустить снижения скорости передачи данных в системе. Один из методов решения этой задачи – сверточное кодирование. Сверточный кодер и декодер Витерби используются совместно для исправления ошибок. Сверточный кодер добавляет избыточность к исходным данным, а декодер Витерби использует декодирование с максимальным правдоподобием для восстановления данных.

Сверточный кодер преобразует входные данные. Скорость кодирования для сверточного кодера составляет 1/2: на каждый входной бит приходится два выходных бита.

Для кодирования каждого выходного бита сверточного кодера используются полиномы генератора, что обеспечивает защиту входных данных от ошибок. Реализация кодера состоит из элементов исключающего ИЛИ (XOR) и сдвиговых регистров.

Декодер Viterbi настроен на те же параметры, что и кодер: кодовая скорость, длина ограничения и полиномы генератора. Мягкое представление данных имеет несколько уровней, отражающих надёжность и, следовательно, уровень достоверности входных данных.

В процессе работы декодера Витерби происходит анализ данных, что позволяет определить, насколько вероятными могут быть значения «1» или «0». Это обеспечивает более надёжную защиту

от ошибок. Выходные данные декодера Витерби представляют собой исходные данные, которые были введены в кодер.

## Описание

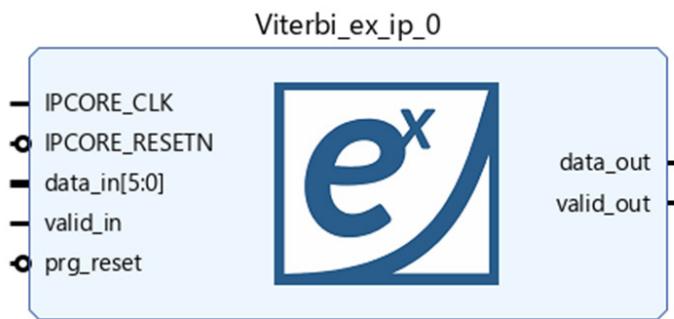

IP-ядро Viterbiex-IP предназначено для решения проблем контроля целостности данных и исправления ошибок в системах радиосвязи. Компания ЦИТМ «Экспонента» разработала архитектуру высокоскоростного декодера, применимого для современных стандартов связи, включая DVB, 3GPP LTE, 3GPP2, IEEE 802.11a/n/ac/ax/be, IEEE 802.16. Архитектура IP-ядра Viterbiex-IP не привязана к конкретному производителю ПЛИС/СБИС, что повышает гибкость и независимость разрабатываемых систем радиосвязи.

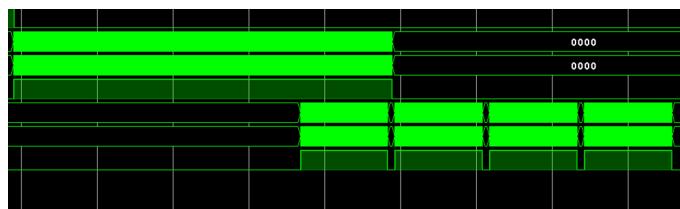

На рисунке 1 представлена зависимость вероятности битовой ошибки от отношения энергии бита к спектральной плотности мощности шума с использованием IP-ядра Viterbiex-IP, а также сравнение с решениями других производителей.

Рисунок 1

Как видно из графика, при использовании IP-ядра Viterbiex-IP вероятность битовой ошибки ниже, чем у аналогичных решений при тестировании с теми же настройками.

# Viterbiex-IP v.1.0

Снижение вероятности битовой ошибки происходит благодаря применению алгоритма поиска минимального элемента и прохождения по решетке в обратном направлении.

IP-ядро Viterbiex-IP оптимизировано для достижения максимальной пропускной способности с минимальными затратами ресурсов и без потери корректирующей функции. Это достигается за счёт оптимизации схемы отбора выживших путей и метода обратного прохода по решетке.

В таблице 1 представлено сравнение с аналогичными решениями от других производителей. Информация взята из открытых источников: Kintex-7 xc7k70/ Zynq®-7000 ZC706/ Kintex-7 xc7k70.

Таблица 1

| Производитель | Xilinx | MathWorks | ЦИТМ<br>Экспонента |

|---------------|--------|-----------|--------------------|

| LUT           | 2210   | 3861      | <b>2347</b>        |

| FF            | 1719   | 2521      | <b>2149</b>        |

| 36k BRAMs     | 2      | 1         | <b>2</b>           |

| Fmax (MHz)    | 281    | 260       | <b>293</b>         |

Также IP-ядро Viterbiex-IP содержит встроенную нормализацию метрик для предотвращения переполнения метрик путей, возникающего в зашумленных каналах.

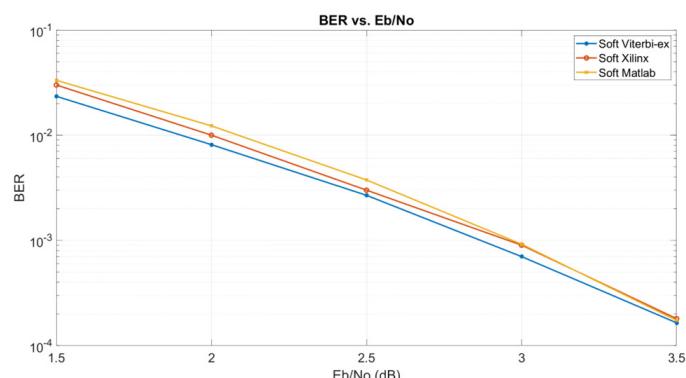

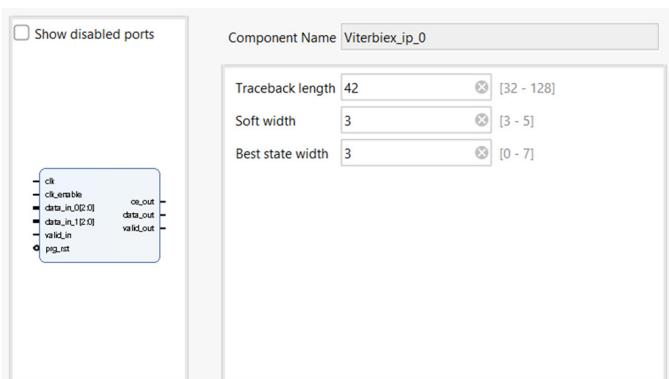

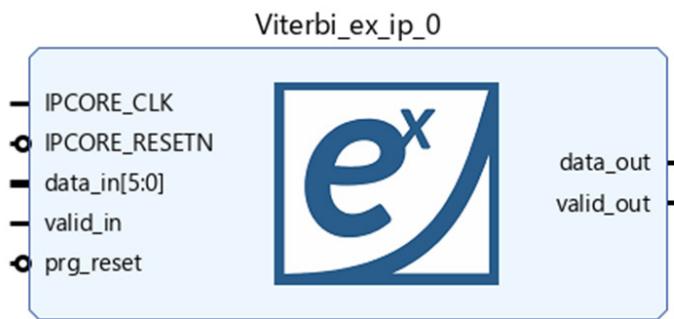

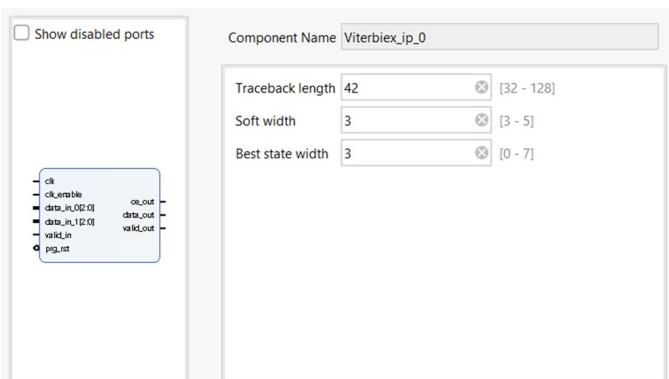

Рисунок 2

Для оптимизации ресурсов и улучшения исправляющей способности декодера при конфигурации IP-ядра можно задать:

- Пользовательские значения длины обратной трассировки

- Разрядность мягких решений на входе

- Число неиспользуемых бит при поиске минимального элемента

Рисунок 3

## Технические характеристики

- Архитектура: мягкое декодирование с параметризируемой длиной входных данных (от 3 до 5 бит)

- Кодовая скорость  $\frac{1}{2}$ , длина кодового ограничения K=7

- Нормализация метрик

- Поддержка пользовательского ввода глубины памяти (traceback length). По умолчанию значение равно 42

- Пользовательская настройка выбора лучшего состояния для декодирования

- Полином генератора  $g1=171, g2=133$

- Latency  $\approx 4 \cdot \text{traceback\_length} + 45$

- Макс. тактовая частота работы ядра – 293 МГц Kintex-7 xc7k70

- LUT – 2347

- FF – 2149

- BRAM – 2

# Viterbiex-IP v.1.0

Снижение вероятности битовой ошибки происходит благодаря применению алгоритма поиска минимального элемента и прохождения по решетке в обратном направлении.

IP-ядро Viterbiex-IP оптимизировано для достижения максимальной пропускной способности с минимальными затратами ресурсов и без потери корректирующей функции. Это достигается за счёт оптимизации схемы отбора выживших путей и метода обратного прохода по решетке.

В таблице 1 представлено сравнение с аналогичными решениями от других производителей. Информация взята из открытых источников: Kintex-7 xc7k70/ Zynq®-7000 ZC706/ Kintex-7 xc7k70.

Таблица 1

| Производитель | Xilinx | MathWorks | ЦИТМ<br>Экспонента |

|---------------|--------|-----------|--------------------|

| LUT           | 2210   | 3861      | <b>2347</b>        |

| FF            | 1719   | 2521      | <b>2149</b>        |

| 36k BRAMs     | 2      | 1         | <b>2</b>           |

| Fmax (MHz)    | 281    | 260       | <b>293</b>         |

Также IP-ядро Viterbiex-IP содержит встроенную нормализацию метрик для предотвращения переполнения метрик путей, возникающего в зашумленных каналах.

Рисунок 2

Для оптимизации ресурсов и улучшения исправляющей способности декодера при конфигурации IP-ядра можно задать:

- Пользовательские значения длины обратной трассировки

- Разрядность мягких решений на входе

- Число неиспользуемых бит при поиске минимального элемента

Рисунок 3

## Технические характеристики

- Архитектура: мягкое декодирование с параметризируемой длиной входных данных (от 3 до 5 бит)

- Кодовая скорость  $\frac{1}{2}$ , длина кодового ограничения K=7

- Нормализация метрик

- Поддержка пользовательского ввода глубины памяти (traceback length). По умолчанию значение равно 42

- Пользовательская настройка выбора лучшего состояния для декодирования

- Полином генератора  $g1=171, g2=133$

- Latency  $\approx 4 \cdot \text{traceback\_length} + 45$

- Макс. тактовая частота работы ядра – 293 МГц Kintex-7 xc7k70

- LUT – 2347

- FF – 2149

- BRAM – 2

# Viterbiex-IP v.1.0

## Интеграция

IP-ядро Viterbiex-IP ЦИТМ Экспонента всегда доступно для целевых платформ FPGA и СБИС. Для специальных применений возможно использование IP-ядра Viterbiex-IP в составе специализированных СнК.

Специалисты ЦИТМ «Экспонента» помогут интегрировать IP-ядра Viterbiex-IP в текущие или будущие проекты и учатут любые требования и пожелания заказчика.

Свяжитесь с нами, чтобы узнать

больше технических подробностей!

+7 (495) 009 65 85

[info@exponenta.ru](mailto:info@exponenta.ru)

[www.exponenta.ru](http://www.exponenta.ru)