# DVB-S2/T2 FEC ENCODEReX-IP v.1.0

## DVB-S2/T2 FEC ENCODER

Системы спутниковой связи требуют постоянного совершенствования. Это связано с тем, что передача информации с помощью спутниковой связи осложняется наличием шумов, интерференции, замираниями сигнала. Из-за этих негативных воздействий данные подвержены искажению без возможности их восстановления.

Для обеспечения целостной передачи данных в системах спутниковой связи используются методы канального кодирования – коды с малой плотностью проверок на чётность (LDPC) и коды БЧХ (BCH), которые вносят избыточность данных для восстановления данных, переданных с ошибкой.

LDPC эффективно корректирует ошибки, вызванные шумами в канале передачи, а BCH за счет алгебраической структуры исправляет остаточные единичные ошибки. Благодаря совместному применению LDPC и BCH обеспечивается безошибочная работа системы на уровне примерно от 0,7 дБ до 1 дБ от предела Шеннона.

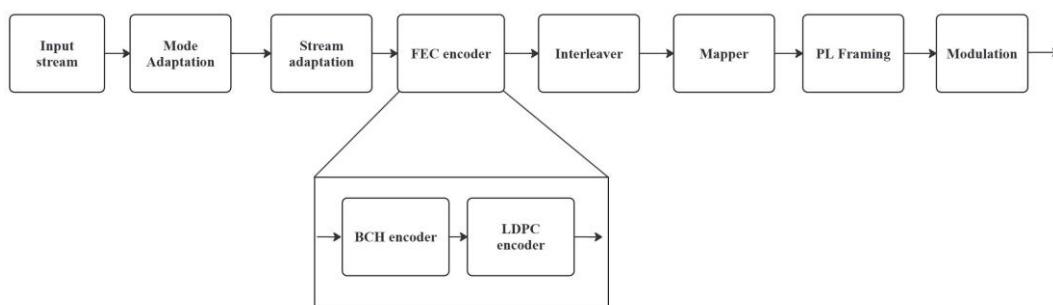

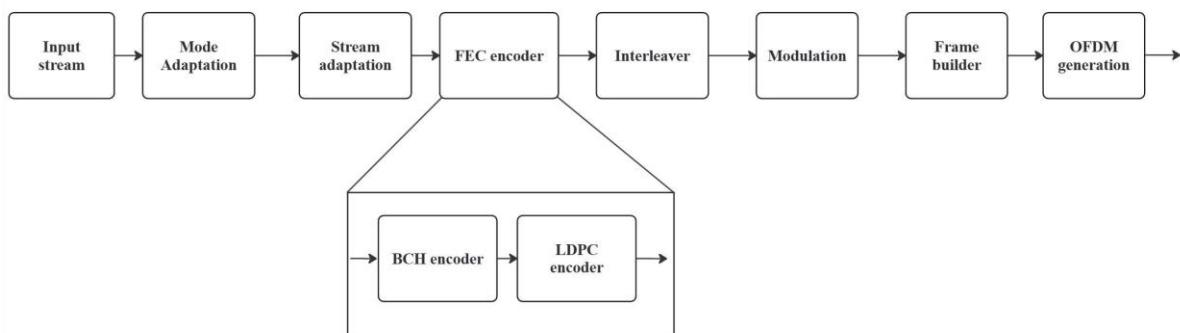

Совместное использование этих методов кодирования было предложено во многих стандартах: DVB-S2, DVB-T2, CCSDS 231.0-B-3. В системах, работающих по стандарту DVB-S2/T2 (рис. 1 и рис. 2), предусмотрено адаптивное кодирование, скорость которого может меняться в зависимости от уровня шумов в канале.

Рис. 1. Структурная схема системы DVB-S2.

Рис. 2) Структурная схема системы DVB-T2.

## ОПИСАНИЕ

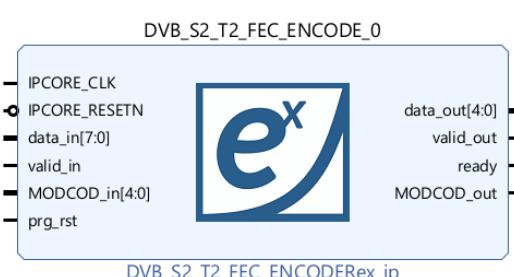

IP-ядро DVB-S2/T2 FEC ENCODEReX-IP предназначено для обеспечения целостной передачи данных в системах спутниковой связи. Компания ЦИТМ «Экспонента» разработала архитектуру высокоскоростного кодера, полностью соответствующую современным стандартам связи DVB-S2 и DVB-T2.

Архитектура IP-ядра не привязана к конкретному производителю ПЛИС/СБИС, что повышает гибкость и независимость, разрабатываемых систем радиосвязи.

Высокоскоростное кодирование осуществляется за счет схемы параллельного кодирования. В блоке BCH реализован параллелизм на 8 бит, а в блоке LDPC – на 360 бит. Благодаря архитектуре параллельного кодирования данных IP-ядро DVB-S2/T2 FEC ENCODEReX-IP оптимизировано для достижения максимальной пропускной способности до 3 Гбит/с, с учетом вывода проверочных битов в правильном порядке.

Одна из особенностей IP-ядра – это изменение кодовой скорости «на лету» в диапазоне от 1/4 до 9/10 в соответствии со стандартами DVB-S2 и DVB-T2, переключение которой осуществляется после завершения этапа кодирования блока длины 64800 бит (Normal FECFRAME).

Функционал IP-ядра и его полное соответствие стандартам позволяет быстро и гибко встраивать его в архитектуру системы связи, представленной на рис.1 и рис.2.

IP-ядро взаимодействует с внешними блоками по процедуре handshake протокола AXI4-Stream для обеспечения целостной передачи данных между блоками.

Таблица 1. Пропускная способность для AMD Zynq xc7z100ffg1156-2 / AMD Ultrascale+ xczu15eg ffvb1156-2-i

| Кодовая скорость | Пропускная способность, Мбит/с |

|------------------|--------------------------------|

| 1/4              | 450/827                        |

| 1/3              | 602/1106                       |

| 2/5              | 724/1330                       |

| 1/2              | 907/1665                       |

| 3/5              | 1089/2000                      |

| 2/3              | 1212/2225                      |

| 3/4              | 1363/2502                      |

| 4/5              | 1454/2670                      |

| 5/6              | 1516/2783                      |

| 8/9              | 1618/2971                      |

| 9/10             | 1638/3008                      |

В таблице 2 представлены аппаратные ресурсы для AMD Zynq xc7z100ffg1156-2 / AMD Ultrascale+ xczu15eg ffvb1156-2-i

Таблица 2.

| Аппаратные ресурсы FPGA | Количество ресурсов |

|-------------------------|---------------------|

| LUT                     | 23445 / 23935       |

| FF                      | 30955 / 30766       |

| BRAM                    | 23.5 / 23.5         |

| Fmax, МГц               | 365 / 670           |

Рис. 3.

## Технические характеристики DVB-S2/T2 FEC ENCODEReX

- Полное соответствие стандартам ETSI EN 302 307 V1.4.1 (2014-07) (DVB-S2) и ETSI EN 302 755 v1.4.1 (2015-07) (DVB-T2)

- Поддержка кадров нормальной длины (Normal FECFRAME, 64800 бит)

- Поддержка кодовых скоростей от 1/4 до 9/10

- **Формирование проверочных битов в правильном порядке**

- Возможность изменения кодовых скоростей от кадра к кадру

- Высокая пропускная способность

- Работа IP-ядра по принципу AXI4-Stream для удобного встраивания в ваш проект

- Задержка 213 тактов

## Интеграция

Дополнительно к IP-ядру может быть поставлен высокоскоростной Interleaver и Scrambler в соответствии со стандартом DVB-S2. IP-ядро DVB-S2/T2 FEC ENCODEReX-IP от ЦИТМ «Экспонента» всегда доступно для целевых платформ FPGA и СБИС.

Для специальных применений возможно использование IP-ядра DVB-S2/T2 FEC ENCODEReX-IP в составе специализированных СнК.

Специалисты ЦИТМ «Экспонента» помогут с интеграцией данного IP-ядра в ваши текущие или будущие проекты в соответствии с любыми требованиями и пожеланиями.

Чтобы обсудить конкретные требования к внедрению IP-ядра в вашу систему связи, пожалуйста, свяжитесь с ЦИТМ «Экспонента».

+7 (495) 009 65 85

info@exponenta.ru

www.exponenta.ru