# OFDMex-IPv1.1

IP-ядро OFDMex-IP предназначено для работы в качестве OFDM-модулятора или OFDM-демодулятора в трактах цифровой обработки сигналов различных систем связи. Данная версия IP-ядра имеет повышенное быстродействие благодаря использованию новой реализации высокопроизводительного потокового алгоритма FFT.

## Применение:

- Системы связи с OFDM-модуляцией: IP-ядро идеально подходит для приемопередающих устройств, использующих технологию OFDM в сочетании с различными стандартами связи.

- Оборудование для систем цифрового телевидения DVB.

- Системы беспроводного доступа Wi-Fi (IEEE 802.11a/n/ac/ax/be).

- Базовые станции 4G/LTE/5G NR: IP-ядро используется для обработки сигналов в базовых станциях мобильной связи, обеспечивая высокую производительность и гибкость конфигурации.

## Архитектура

IP-ядро OFDMex-IP предоставляет пользователю возможность конфигурации с целью выбора режима работы и максимальной длины FFT. Последнее позволяет в случае необходимости оптимизировать используемые ресурсы FPGA. При конфигурации доступен выбор режима работы OFDM-модулятор или OFDM-демодулятор. Максимальная длина FFT может быть установлена из ряда: 64, 128, 256, 512, 1024, 2048.

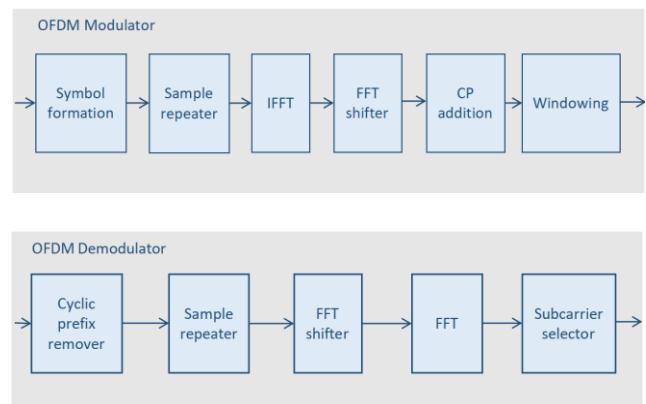

На рис. 1 показаны структурные схемы ядра в режиме модулятора и демодулятора.

При работе в режиме модулятора IP-ядро принимает на вход комплексные отсчеты, формирующие спектр OFDM-символа. Полный спектр формируется с помощью формирователя OFDM-символа (Symbol formation) с учётом требуемого размера защитных интервалов. Далее с помощью повторителя (Sample repeater) в случае, если длина FFT меньше максимальной длины, формируется полный набор отсчетов для обратного преобразования Фурье (IFFT). Поскольку входные данные модулятора представлены как симметричный спектр, спектр сигнала на выходе IFFT смещается на половину частоты дискретизации. После этого к OFDM-символу во временной области добавляется циклический префикс требуемой длины. В случае использования оконной обработки в конце также добавляется суффикс с длиной, равной длине окна. Кроме того, в начале префикса и для суффикса применяется умножение на оконную функцию (Windowing). В выходной последовательности префикс перекрывается с суффиксом предыдущего символа.

Рис. 1.

При работе в режиме демодулятора IP-ядро принимает на входе OFDM-символы во временной области. При этом сначала происходит удаление циклического префикса. Далее, если длина символа меньше максимального размера FFT, с помощью периодического повторения формируется последовательность длины, необходимой для FFT. Так как отсчеты на выходе демодулятора интерпретируются как симметричный

спектр, перед FFT во временной области спектр сигнала смещается на половину частоты дискретизации. После выполнения преобразования Фурье из спектра выделяются необходимые компоненты и подаются на выход.

### Сигналы управления и временные диаграммы

Обработка поступающих на входные порты данных начинается после установки сигнала valid\_in в значение логической «1». Полезные выходные данные появляются после установки valid\_out в значение логической «1». Управляющий порт fft\_mode определяет размер FFT/IFFT преобразования для текущего OFDM-символа. Номер режима выбирается из ряда: 0, 1, 2, 3, 4, 5, что соответствует длине FFT 64, 128, 256, 512, 1024, 2048 соответственно. С помощью портов cp\_len, left\_guard, right\_guard задаются соответственно длина циклического префикса, размер левого и правого защитного интервала. Порт dc\_null в режиме модулятора используется для установки режима автоматической вставки отсчёта нулевой постоянной составляющей. В режиме демодулятора порт dc\_null используется для установки режима удаления отсчёта постоянной составляющей из выходных данных. В режиме модулятора существует дополнительный порт win\_len для установки длины окна при оконной обработке. Максимальная длина окна – win\_len = 32 отсчёта. При установке длины win\_len = 0 оконная обработка не выполняется. Также предусмотрен порт сброса состояния IP-ядра OFDMex-IP – prg\_RST, по сигналу от которого происходит общий сброс всех регистров внутри блока.

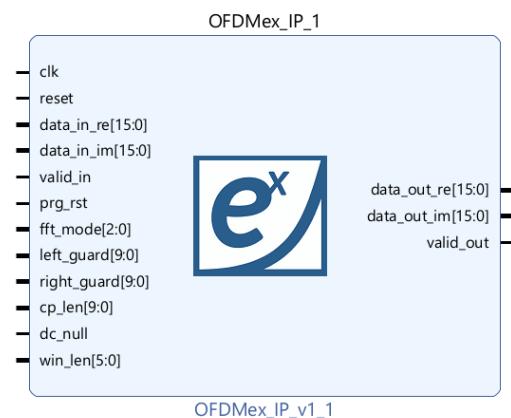

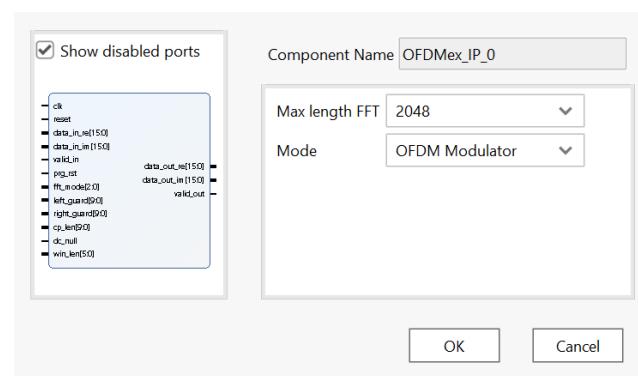

На рис. 2 показан пример дизайна системы с использованием IP-ядер OFDMex-IP. При конфигурации ядер пользователю необходимо указать режим работы ядра и максимальную длину FFT (рис. 3)

OFDMex\_IP\_v1\_1

Рис. 2.

Рис. 3.

Обработка данных в ядре OFDMex-IP имеет высокую степень конвейеризации. Задержка данных между входом и выходом зависит от конфигурации и значений текущих параметров. Запуск цикла обработки OFDM-символа происходит после того, как на вход ядра поступят все данные, необходимые для формирования или демодуляции.

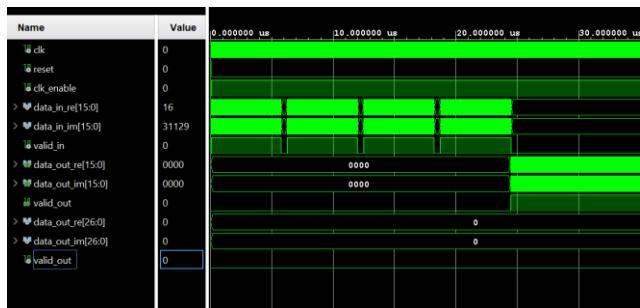

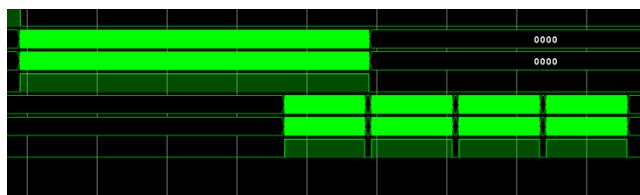

На рис. 4 показан пример временных диаграмм работы модулятора. На вход модулятора непрерывно поступают данные для последовательного формирования четырех OFDM-символов. Как видно, данные на выходе появляются с задержкой, обусловленной конвейерной обработкой.

Рис. 4

Аналогичным образом выглядят временные диаграммы работы в режиме демодулятора (Рис. 5).

Рис. 5.

## Совместимость со стандартом LTE

IP-ядро OFDMex-IP может быть использовано в системах связи стандарта LTE с количеством ресурсных блоков (NDLRB): 6, 15, 25, 50, 100. Для этого необходимо сконфигурировать ядро на максимальную длину FFT 2048 и обеспечить подачу на входные порты соответствующих параметров исходя из стандарта. Например, для NDLRB = 50 в режиме extended CP следует установить параметры: fft\_mode = 4, dc\_null = 1, cp\_len = 256, left\_guard = 212, right\_guard = 211.

## Технические характеристики OFDMex-IP

- Режимы работы:

- OFDM-модулятор

- OFDM-демодулятор

- Максимальное значение длины FFT, устанавливаемое при конфигурации - 64, 128, 256, 512, 1024, 2048

- Значение длины FFT, устанавливаемое через порт, - 64, 128, 256, 512, 1024, 2048 ( $\text{fft\_len} \leq \text{FFTmax}$ )

- Максимальная длина окна при оконной обработке в модуляторе – 32 (по стандарту IEEE 802.11g)

Следующие параметры IP-ядра зависят от конкретной конфигурации. Для справки приведены некоторые значения.

### Модулятор, FFTmax = 64

- Максимальная тактовая частота работы ядра – 405 МГц (Xilinx Zynq7100-2)

- LUT – 3074

- DSP – 10

- FF – 7124

- RAMB36E1 - 1.5

### Модулятор, FFTmax = 2048

- Максимальная тактовая частота работы ядра – 405 МГц (Xilinx Zynq7100-2)

- LUT – 4684

- DSP – 19

- FF – 11526

- RAMB36E1 – 19

### Демодулятор, FFTmax = 64

- Максимальная тактовая частота работы ядра – 410 МГц (Xilinx Zynq7100-2)

- LUT – 3119

- DSP – 6

- FF – 6542

- RAMB36E1 - 0.5

### Демодулятор, FFTmax = 2048

- Максимальная тактовая частота работы ядра – 409 МГц (Xilinx Zynq7100-2)

- LUT – 5860

- DSP – 18

- FF – 12689

- RAMB36E1 - 19

## Тестирование и симуляция

Для тестирования и симуляции IP-ядра OFDMex-IP возможна поставка завершенного тестового окружения, реализованного с помощью языков описания Verilog/VHDL с привязкой к конкретному типу симулятора: Mentor Graphics ModelSim/Cadence Incisive/Xilinx Vivado Simulator.

## Интеграция

IP-ядро OFDMex-IP ЦИТМ «Экспонента» всегда доступно для целевых платформ FPGA и СБИС. При наличии специфических требований возможно рассмотрение доработки ядра. Для специальных применений возможно использование IP-ядра OFDMex-IP в составе специализированных СнК.

Специалисты ЦИТМ «Экспонента» помогут интегрировать IP-ядро OFDMex-IP в текущие или будущие проекты и учтут любые требования и пожелания заказчика.

Чтобы обсудить ваши конкретные требования к внедрению, пожалуйста, свяжитесь с ЦИТМ «Экспонента» +7 (495) 009 65 85 | info@exponenta.ru | www.exponenta.ru