# VITERBIex-IP v.1.1

## Сверточное декодирование Витерби

В современных системах связи критически важна надёжная передача данных с возможностью восстановления информации при наличии помех и искажений. Это позволяет минимизировать количество повторных передач, обусловленных ошибками, что, в свою очередь, способствует увеличению эффективности и пропускной способности канала связи. Одним из широко применяемых методов для обеспечения коррекции ошибок является сверточное кодирование. Сверточный кодер совместно с декодером Витерби реализует механизм коррекции ошибок, основанный на добавлении избыточности и использования алгоритма максимального правдоподобия.

Сверточный кодер преобразует входную битовую последовательность, добавляя к ней избыточные биты в соответствии с заданной структурой. При этом применяется определённая скорость кодирования — в данном случае 1/2, что означает генерацию двух выходных битов на каждый входной бит.

Декодирование осуществляется алгоритмом Витерби, который на основе принципа максимального правдоподобия восстанавливает наиболее вероятную исходную последовательность битов, компенсируя влияние ошибок, возникших в канале передачи.

## Описание

IP-ядро VITERBIex-IP, разработанное компанией ЦИТМ «Экспонента», предназначено для обеспечения контроля целостности и коррекции ошибок в системах цифро-

вой радиосвязи. Архитектура ядра представляет собой высокопроизводительный декодер Витерби, ориентированный на применение в современных телекоммуникационных стандартах, включая DVB, 3GPP LTE, 3GPP2, IEEE 802.11a/n/ac/ax/be, IEEE 802.16. Ключевым преимуществом решения является аппаратная независимость: Архитектура IP-ядра не привязана к конкретному производителю ПЛИС/СБИС, что повышает гибкость и независимость, разрабатываемых систем радиосвязи.

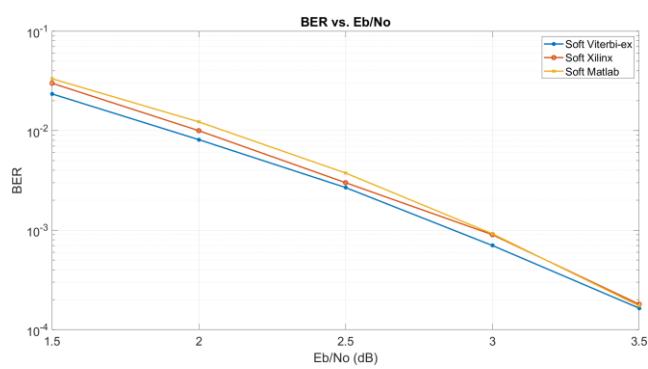

На Рис.1 представлена зависимость вероятности битовой ошибки (BER) от отношения энергии бита к спектральной плотности мощности шума ( $E_b/N_0$ ) при использовании IP-ядра VITERBIex-IP, а также приведено сравнение с аналогичными решениями сторонних производителей.

Рис.1

Как видно из графика, IP-ядро VITERBIex-IP демонстрирует более низкий уровень BER по сравнению с аналогами при идентичных условиях моделирования, что указывает на его высокую эффективность в условиях зашумленных каналов.

Высокая пропускная способность достигается благодаря архитектурным улучшениям в механизме хранения и отбора выживших путей, а также оптимизации логики трассировки обратного пути, что позволяет обеспечить высокую скорость работы.

В таблице 1 представлено сравнение с аналогичными решениями от других производителей. Информация взята из открытых источников: AMD Kintex-7 xc7k70/ AMD Zynq®-7000 ZC706/AMD Kintex-7 xc7k70

**Таблица 1.**

| Производитель          | Xilinx | MathWorks | ЦИТМ Экспонента |

|------------------------|--------|-----------|-----------------|

| LUT                    | 2210   | 3861      | <b>2289</b>     |

| FF                     | 1719   | 2521      | <b>2105</b>     |

| 36k BRAMs              | 2      | 1         | 2               |

| F <sub>max</sub> , МГц | 281    | 260       | <b>290</b>      |

IP-ядро VITERBlex-IP также включает встроенный механизм **нормализации метрик**, предназначенный для предотвращения переполнения путевых метрик, что актуально при работе в условиях низкого отношения сигнал/шум.

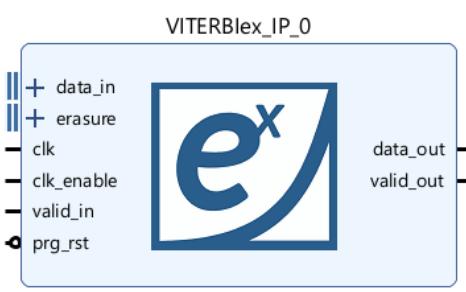

Рис.2

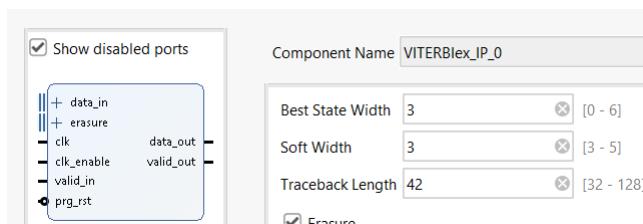

Для повышения эффективности использования аппаратных ресурсов и улучшения корректирующей способности, архитектура IP-ядра поддерживает широкие возможности параметризации: длина обратной трассировки, разрядность мягких решений на выходе, число игнорируемых бит при поиске минимального элемента

Рис.3

Свяжитесь с нами, чтобы узнать больше технических подробностей!

## Технические характеристики VITERBlex-IP

- Архитектура: Мягкое декодирование с параметризуемой длиной входных данных (от 3 до 5 бит)

- Кодовая скорость 1/2, длина кодового ограничения K=7

- Нормализация метрик

- Выкашивание символов

- Полная совместимость со стандартами: DVB, 3GPP LTE, 3GPP2, IEEE 802.11a/n/ac/ax/be, IEEE 802.16

- Поддержка пользовательского ввода глубины памяти (traceback length)

- Пользовательская настройка выбора лучшего состояния для декодирования

- Полином генератора g1=171, g2=133

- Задержка  $\approx 4 \cdot \text{traceback\_length} + 45$

- Макс. тактовая частота работы ядра – 290 МГц Kintex-7 xc7k70

- LUT – 2289

- FF – 2105

- BRAM - 2

## Интеграция

IP-ядро VITERBlex-IP ЦИТМ Экспонента, всегда доступно для целевых платформ FPGA и СБИС. Для специальных применений возможно использование IP-ядра в составе специализированных СнК. Интеграция IP-ядра VITERBlex-IP в текущие или будущие проекты возможна в соответствии с любыми требованиями и пожеланиями заказчика, силами специалистов ЦИТМ Экспонента.

Чтобы обсудить ваши конкретные требования к внедрению, пожалуйста, свяжитесь с ЦИТМ Экспонента

+7 (495) 009 65 85

info@exponenta.ru

www.exponenta.ru