IP-ядро DPDex-IP

Современные и проектируемые системы радиосвязи (3G/4G/5G, LTE/LTE-A, Wi-Fi 802.11n/ac/ax), предназначенные для передачи больших объёмов информации, предполагают использование каналов с высокой спектральной эффективностью (бит/(с×Гц)).

В свою очередь высокая спектральная эффективность, как правило, приводит к высокому уровню пик-фактора формируемого сигнала (PAPR>3 дБ). Всё это накладывает жёсткие требования к линейности радиопередающего тракта (ACPR, ACLR, EVM), что приводит к увеличению стоимости, габаритов и одновременно к снижению КПД всей системы радиосвязи.

В течение последних нескольких лет инженеры Экспоненты исследовали и разрабатывали системы ввода цифровых предыскажений DPD (Digital Predistortion). Разработка алгоритмов DPD – сложная задача, требующая большого количества времени и ресурсов. При этом конечный результат может потребовать значительных вычислительных ресурсов от целевой платформы.

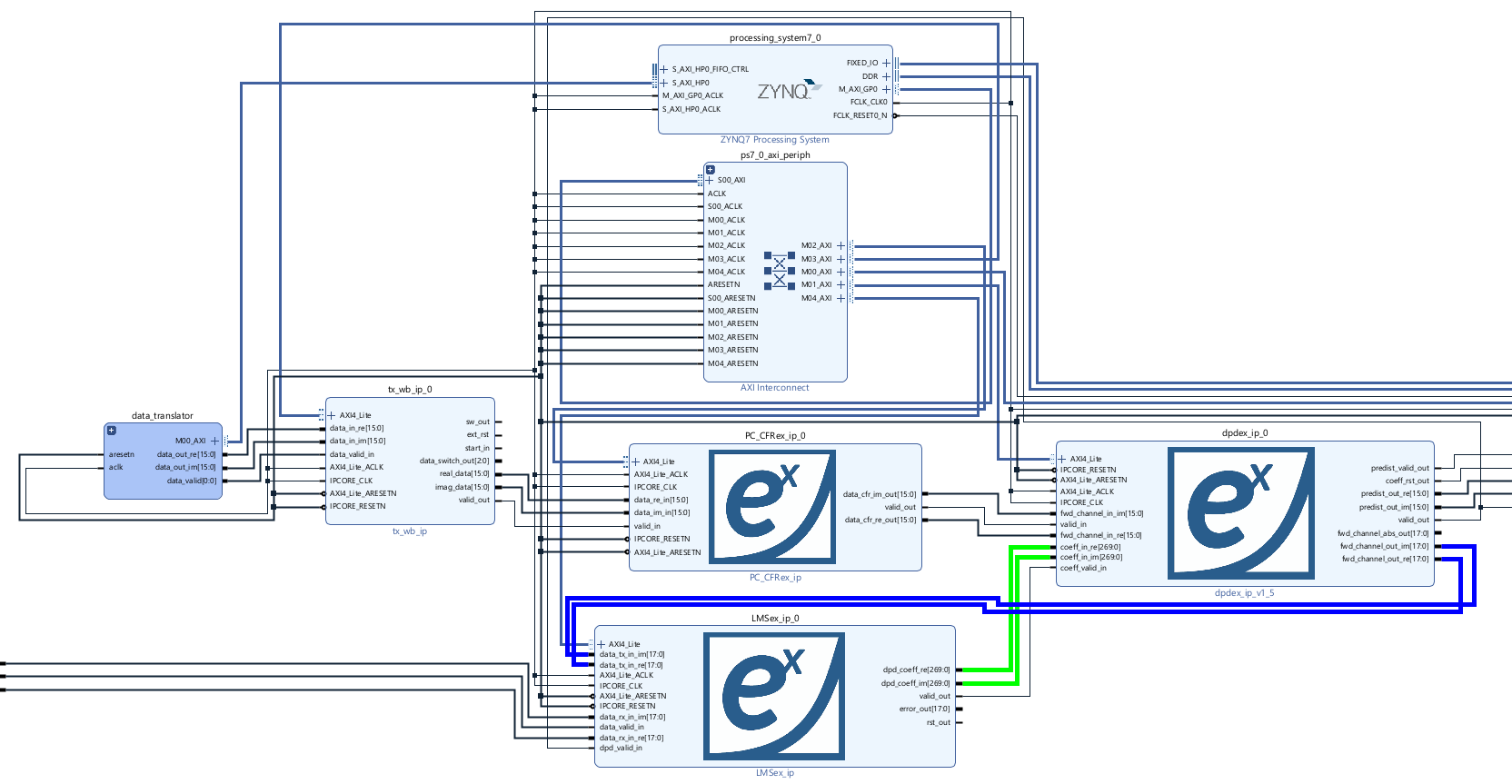

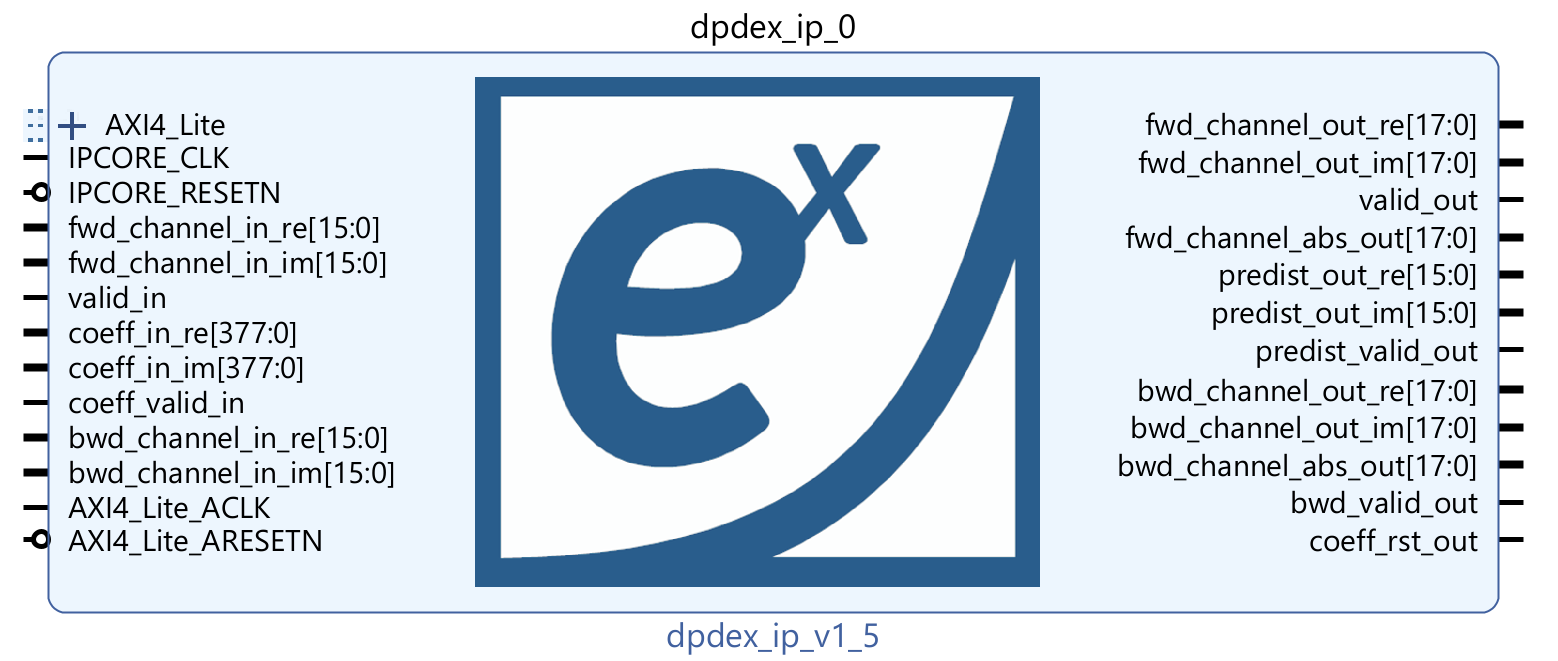

Архитектура IP-ядра DPDex-IP не привязана к конкретному производителю ПЛИС/СБИС, что повышает гибкость и независимость разрабатываемых систем радиосвязи.

Технические характеристики DPDex-IP

Максимальная полоса предыскажаемого сигнала – 220 МГц

Максимальная тактовая частота работы ядра – 450 МГц (Xilinx Zynq7100/ Zynq7045/Kintex-7).

IP-ядро DPDex-IP реализовано с учётом максимальных требований к быстродействию и производительности. ЦИТМ Экспонента предлагает улучшенную реализацию архитектуры ввода цифровых предыскажений – «Memory Polynomial Advanced». Улучшения архитектуры коснулись быстродействия, точности вычислений, минимизации вычислительных ресурсов. Основным преимуществом IP-ядра DPDex-IP является возможность предыскажения сверхширокополосных сигналов (до 220 МГц).

Степень подавления уровня помехи в соседнем канале (ACLR/ACPR) зависит от качества рассчитанных коэффициентов предыскажения, нелинейных свойств усилителя мощности, полосы предыскажаемого сигнала.

Для тестирования и симуляции IP-ядра DPDex-IP возможна поставка завершённого тестового окружения реализованного с помощью языков описания Verilog/VHDL с привязкой к конкретному типу симулятора: Mentor Graphics ModelSim/Cadence Incisive/Xilinx Vivado Simulator.

Интеграция IP-ядер от ЦИТМ Экспонента в ваш проект

IP-ядра DPDex-IP от ЦИТМ Экспонента доступны для целевых платформ FPGA и СБИС. Для специальных применений возможно использование указанных IP-ядер в составе специализированных СнК.

Интеграция DPDex-IP в текущие или будущие проекты возможна в соответствии с любыми требованиями и пожеланиями заказчика и производится силами инженеров ЦИТМ Экспонента.

Используйте в вашем проекте протестированные, оптимизированные, безопасные IP-ядра, а также техническую поддержку и помощь в настройке и интеграции этих решений от ЦИТМ Экспонента. IP-ядра разработаны в России, выполняют требования импортозамещения и могут быть использованы как с импортной, так и с российской электронной компонентной базой. Мы проконсультируем вас по выбору и внедрению IP-ядра в ваш проект и поможем довести работы до полного соответствия техническому заданию проекта.

Скачать datasheet по DPDex-IP

Скачать datasheet по DPDex-IP