Генерация HDL описания для ПЛИС (SLHL)

Что входит в курс:

- Подготовка моделей Simulink к генерации HDL-кода;

- Генерация HDL-кода и тестбенча для модели Simulink;

- Осуществление оптимизации по скорости и площади;

- Интеграция рукописного кода и существующих IP;

- Верификация сгенерированного HDL-кода с использованием тестбенчей и ко-симуляции.

Предварительная подготовка:

Курс Цифровая обработка сигналов в Simulink или подобный опыт работы в Simulink.

Продолжительность курса - 2 дня.

Программа

День 1

- Подготовка моделей Simulink для генерации HDL-кода.

- Анализ кода и перевод в арифметику с фиксированной точкой.

- Оптимизация сгенерированного HDL-кода.

День 2

- Генерация HDL-кода из блока MATLAB Function.

- Совместное использование внешнего и сгенерированного HDL-кода.

- Генерация HDL-кода для многоскоростных моделей.

- Верификация HDL-кода посредством ко-симуляции.

Подготовка моделей Simulink для генерации HDL-кода

Цель: Подготовить модель к генерации HDL-кода. Получить HDL код и тестбенч для простых моделей, не требующих оптимизации.

- Подготовка моделей Simulink для генерации HDL-кода;

- Генерация HDL-кода;

- Генерация тестбенча;

- Верификация сгенерированного кода при помощи HDL-симулятора.

Анализ кода и перевод в арифметику с фиксированной точкой

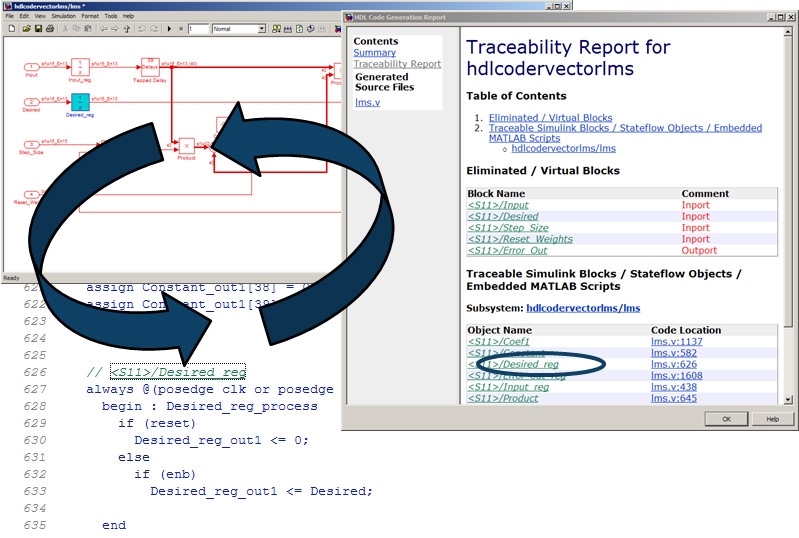

Цель: Установить соответствие между генерируемым HDL-кодом и конкретными блоками в модели Simulink. Использовать инструмент Fixed-Point Tool для построения окончательной архитектуры модели в арифметике с фиксированной точкой.

- Привязка сгенерированного HDL-кода к конкретным блокам Simulink;

- Повышение эффективности и точности HDL-кода с Fixed-Point Tool.

Оптимизация сгенерированного HDL-кода

Цель: Использовать конвейеризацию для удовлетворения требованиям по скорости проекта. Использовать конкретные аппаратные реализации и совместное использование ресурсов для оптимизации по площади.

- Генерация HDL-кода с инструментом HDL Workflow Advisor;

- Удовлетворение требованиям по скорости посредством конвейеризации;

- Выбор подходящей аппаратной реализации для совместимых блоков Simulink;

- Совместное использование ресурсов ПЛИС/ASIC в подсистемах;

- Верификация того, что оптимизированный код верен до бита на каждом такте.

Генерация HDL-кода из блока MATLAB Function

Цель: Сгенерировать HDL-код, в том случае когда часть проекта написана в MATLAB с использованием блока MATLAB Function. Научиться использовать блоки из библиотеки шаблонов в вашем проекте. Написать код MATLAB для операций в арифметике с фиксированной точкой.

- Использование библиотеки шаблонов;

- Генерация HDL-кода из блоков MATLAB Function.

Совместное использование внешнего и сгенерированного HDL-кода

Цель: Интегрировать рукописный HDL-код и/или готовые IP-ядра в ваш проект.

- Интеграция внешнего HDL-кода;

- Интеграция сторонних IP-ядер.

Генерация HDL-кода для многоскоростных моделей

Цель: Сгенерировать HDL-код для многоскоростных систем.

- Подготовка многоскоростной модели для кодогенерации;

- Генерация HDL-кода с одним или несколькими источниками тактовой частоты.

Верификация HDL-кода посредством ко-симуляции

Цель: Верифицировать ваш HDL-код используя HDL-симулятор в модели Simulink.

- Верификация компонент HDL в Simulink.

Simulink

Simulink Сертификация и разработка систем повышенной надежности

Сертификация и разработка систем повышенной надежности Проектирование систем цифровой обработки сигналов (SLBE-G)

Проектирование систем цифровой обработки сигналов (SLBE-G) Радио ГИГАБИТ - Разработка модема на ПЛИС для радиорелейной системы связи миллиметрового диапазона с использованием методологии модельно-ориентированного проектирования

Радио ГИГАБИТ - Разработка модема на ПЛИС для радиорелейной системы связи миллиметрового диапазона с использованием методологии модельно-ориентированного проектирования