Wireless HDL Toolbox

Wireless HDL Toolbox предоставляет набор подготовленных для реализации на FPGA и ASIC блоков, реализующих работу подсистем и модулей стандарта LTE. Алгоритмы из данного toolbox’а, шлюзы между стандартными блоками и модулями, предназначенными для преобразования в HDL код, готовые опорные проекты, позволяют максимально быстро приступить к разработке и верификации систем связи LTE в среде Simulink.

Опорные проекты, представленные в данном инструментарии полностью открыты, доступны для изменений и могут быть модифицированы под ваши задачи. Алгоритмы, собранные в данном toolbox’е, оптимизированы для реализации на базе платформ FPGA и ASIC и позволяют строить не только прототипы, но и готовые к внедрению системы.

Алгоритмы из Wireless HDL Toolbox разработаны для генерации читаемого Verilog и VHDL кода, и построены оптимальным для синтеза образом. Кроме того, совместно с Communications Toolbox вы можете совместить разработанные модели с SDR платформами для полунатурного моделирования и тестирования разработанных алгоритмов на реальных сигналах.

Сервис «Разработка систем связи» (рус.)

Опорные реализации подсистем LTE

Встраивайте в свои проекты подготовленные, протестированные на FPGA, модули и подсистемы для ускорения процесса разработки.

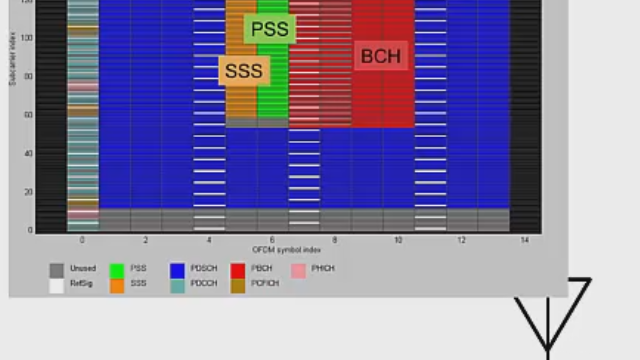

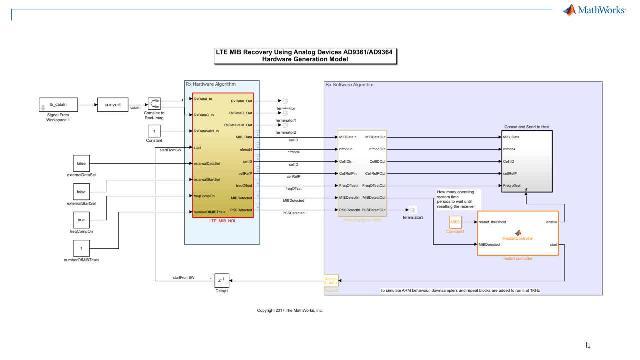

Процедура поиска соты, выделение MIB и SIB1

Используйте данный набор подсистем для демодуляции и декодирования сигналов от реальных eNodeB, с последующим выделением Master Information Block (MIB) и System Information Block (SIB 1) в Ваших FPGA и ASIC разработках. Данные подсистемы поддерживают режимы TDD и FDD и были проверены на работоспособность в реальных проектах инженерами из многих стран мира.

Передовые техники формирования сигналов F-OFDM

Изучите данный опорный проект, чтобы разобраться в тонкостях реализации F-OFDM модуляции, которая используется в стандарте связи 5-го поколения. Данная технология применяется после обратного преобразования Фурье для улучшения спектральной маски сигнала, при сохранении ортогональности поднесущих.

Используйте IP блоки (ядра), реализующие подсистемы LTE

Ускорьте вашу разработку, применяя аппаратно-верифицированные IP блоки, реализующие подсистемы и алгоритмы LTE стандарта.

LTE IP блоки

Набор IP блоков из Wireless HDL Toolbox позволит вам моделировать и проводить симуляцию с использованием оптимизированных для синтеза HDL-кода блоков, реализующих такие алгоритмы как сверточное, турбо или CRC кодирование, а также OFDM модуляторы и демодуляторы. Построив и протестировав систему из данных блоков, вы можете реализовать ее с использованием HDL Coder, получив синтезируемый и читаемый Verilog или VHDL-код.

Универсальные (Multistandard) IP блоки

Используйте аппаратно-верифицированные IP-блоки, такие как Витерби декодер или БПФ с переменным шагом для разработки беспроводных систем связи различных стандартов, включая LTE, WLAN, DVB, WiMAx, HiperLAN, а также спутниковых линий связи.

Верификация с использованием опорных проектов

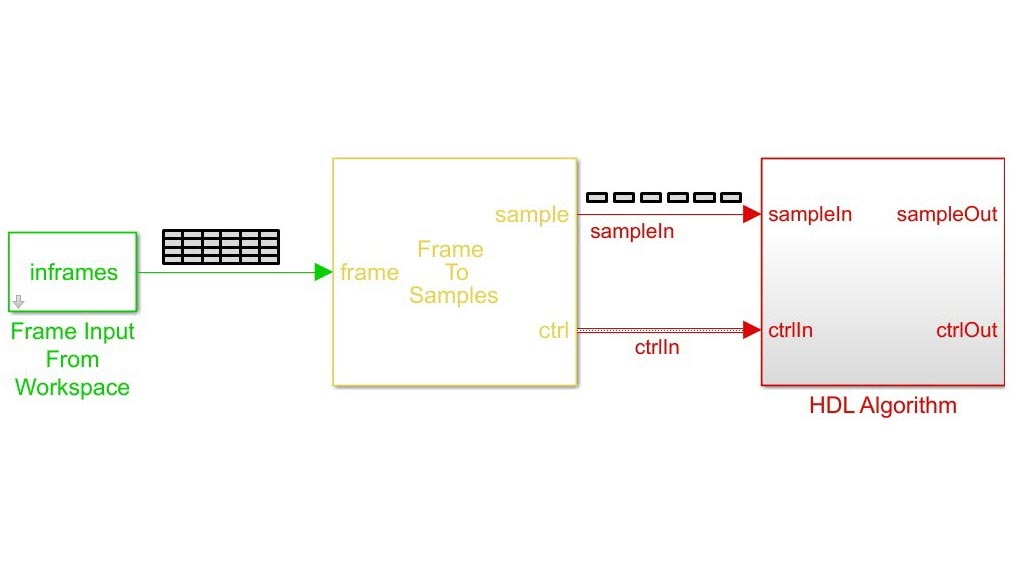

Совмещайте работающие с блоками данных алгоритмы Simulink с тестовыми сценариями или оптимизированными для синтеза HDL-кода потоковыми алгоритмами, работающими с отсчетами, для более эффективной верификации.

Переход между кадрами и отсчетами

Преобразовывайте построенные из блоков данных сигналы MATLAB и LTE Toolbox в потоки отсчетов с набором сигналов управления для реализации на FPGA. Затем проводите обратное преобразование результатов обработки сигналов в вашем устройстве в кадры для верификации работы устройства с использованием опорных проектов, полностью соответствующих требованиям LTE стандарта.

Опорные проекты и шаблоны для изучения работы LTE и верификации ваших разработок

Изучите возможности верификации ваших аппаратных разработок с применением алгоритмов из LTE Toolbox а также различных тестов.

Преобразовывайте построенные из блоков данных сигналы MATLAB и LTE Toolbox в потоки отсчетов с набором сигналов управления для реализации на FPGA. Затем проводите обратное преобразование результатов обработки сигналов в вашем устройстве в кадры для верификации работы устройства с использованием опорных проектов, полностью соответствующих требованиям LTE стандарта.

Полунатурное моделирование с использованием FPGA платформ

Используйте HDL Verifier для верификации ваших разработок, а также подключайте к MATLAB Simulink отладочные платформы FPGA для верификации с применением HIL технологий.

Портирование разработанных и в среде MATLAB Simulink алгоритмов и систем на платформы FPGA, ASIC или SOC

Переносите ваши разработки на платформу FPGA для тестирования и верификации с использованием реальных сигналов из радиоэфира, используйте разработанные модели для реализации как прототипов, так и серийных изделий.

Применение SDR платформ

Стройте прототипы беспроводных систем связи и исследуйте работу эталонных проектов, реализующих подсистемы LTE, в железе с использованием пакетов поддержки Zynq SDR для Communications Toolbox.

Внедрение разработок

Используйте HDL-кодер для генерации высокоэффективных, платформонезависимых HDL модулей с AXI интерфейсами ввода – вывода.

Новые возможности

Модулятор OFDM

Формируйте сигналы с ортогональным частотным разделением в полном соответствии с LTE стандартом.

Опорные проекты LTE передатчиков

Формируйте сигналы LTE содержащие PSS, SSS, cell-specific информацию, а также MIB.

Пример 1536-точечного БПФ

Реализуйте 1536 точечное БПФ с использованием одного 512-точечного БПФ блока.

LTE и 5G NR символьные модуляторы

Модулируйте биты сообщений в точном соответствии со стандартами LTE или 5G.

Документация

Документация

Выделение MIB блока и поиск соты

Выделение MIB блока и поиск соты

Генерация HDL-кода с применением Wireless HDL Toolbox

Генерация HDL-кода с применением Wireless HDL Toolbox HDL Coder

HDL Coder

HDL Verifier

HDL Verifier

Пакет поддержки Zynq SDR для Communications Toolbox

Пакет поддержки Zynq SDR для Communications Toolbox Проектирование физического уровня систем связи стандартов LTE и LTE Advanced (MLTE)

Проектирование физического уровня систем связи стандартов LTE и LTE Advanced (MLTE)