Автоматическая генерация кода для Zynq (SLZQ)

Что входит в курс:

-

Обзор платформы Zynq и настройка среды;

-

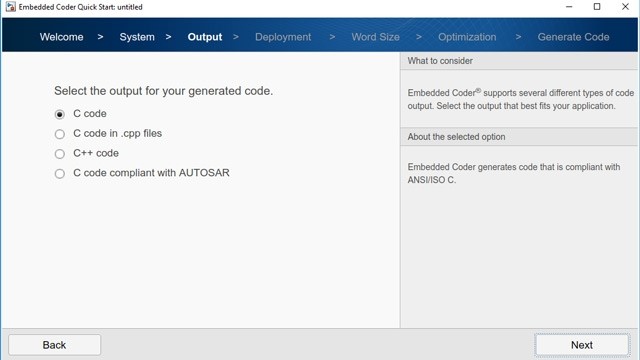

Введение в Embedded Coder и HDL Coder;

-

Генерация и развёртывание IP-ядра;

-

Использование интерфейса AXI4;

-

Верификация в режиме «процессор-в-контуре» (PIL);

-

Обмен данными с приложениями реального времени;

-

Интеграция драйверов;

-

Пользовательский reference design.

Предварительная подготовка:

- Курсы MATLAB для профессионалов (MLBE), Проектирование систем цифровой обработки сигналов (SLBE-G), Генерация HDL описания для ПЛИС (SLHL), Генерация C/C++ кода для встраиваемых систем (SLEC).

- Знание языка программирования C и языков описания аппаратуры (HDL).

Продолжительность курса - 2 дня.

Программа

День 1

- Обзор платформы Zynq и настройка среды.

- Введение в Embedded Coder и HDL Coder.

- Генерация и развёртывание IP ядра.

- Использование интерфейса AXI4.

- Верификация в режиме «процессор-в-контуре».

День 2

- Обмен данными с приложениями реального времени.

- Интеграция драйверов устройств.

- Пользовательский Reference Design.

- Приложение A: Объект Zynq и команды Linux.

- Приложение B: арифметика с фиксированной точкой.

Обзор платформы Zynq и настройка среды

Цель: сконфигурировать платформу Zynq-7000 и настроить среду MATLAB.

-

Обзор Zynq-7000;

-

Наладка платформы Zynq, установка ПО;

-

Настройка среды MATLAB;

-

Проверка соединения с устройством Zynq.

Введение в Embedded Coder и HDL Coder

Цель: сконфигурировать модель Simulink для генерации встраиваемого кода и эффективно интерпретировать сгенерированный код.

-

Архитектура встраиваемого приложения;

-

Генерация ERT-кода (embedded real-time code);

-

Модули кода;

-

Структуры данных в сгенерированном коде;

-

Подготовка модели Simulink к автоматической генерации HDL-кода;

-

Использование HDL Workflow Advisor.

Генерация и развёртывание IP ядра

Цель: использовать HDL Workflow Advisor для конфигурации модели Simulink, осуществить генерацию и сборку HDL- и C-кода, выполнить программирование платформы Zynq.

-

Конфигурирование подсистемы для программируемой логики;

-

Конфигурирование интерфейсов конечного и периферийных устройств;

-

Генерация IP ядра и интеграция с EDK;

-

Сборка и развёртывание битового потока ПЛИС;

-

Генерация и развёртывание модели программного интерфейса;

-

Изменение параметров в режиме External Mode.

Использование интерфейса AXI4

Цель: использовать различные интерфейсы AXI для обмена данными между процессорной системой и программируемой логикой.

-

Обзор интерфейса AXI;

-

Приложения AXI4-Lite;

-

Использование AXI4-Stream;

-

Производительность AXI4.

Верификация в режиме «процессор-в-контуре»

Цель: использовать режим «процессор-в-контуре» для верификации алгоритма, запущенного на платформе Zynq, и оценить время исполнения вашего алгоритма.

-

Рабочий процесс верификации в режиме «процессор-в-контуре» (PIL) на Zynq;

-

PIL-верификация с model reference;

-

Профилирование выполнения кода с PIL;

-

Анализ режима PIL.

Обмен данными с приложениями реального времени

Цель: использовать интерфейс UDP для организации потоковой передачи данных между Simulink и приложением реального времени, исполняемого на платформе Zynq.

-

Обзор интерфейса обмена данными;

-

Настройка блоков UDP для потоковой передачи;

-

Синхронизация данных между Simulink и Zynq;

-

Обмен данными с AXI Stream;

-

Разделение проекта;

-

Анализ интерфейсов обмена данными.

Интеграция драйверов устройств

Цель: разработать драйверы для подключения периферийных устройств к процессорной системе.

-

Рабочий процесс разработки драйверов устройств;

-

Использование Legacy Code Tool;

-

GPIO интерфейс;

-

Кросс-компиляция драйверов устройств.

Пользовательский Reference Design

Цель: создать и упаковать повторно используемое IP-ядро для Vivado, зарегистрировать пользовательские платы и проекты (reference designs).

-

Для чего создавать пользовательские reference design;

-

Создание IP-ядра для Vivado;

-

Обзор reference design;

-

Настройка reference design;

-

Регистрация пользовательской платы и проекта (reference design).

Приложение A: Объект Zynq и команды Linux

-

Объект Zynq;

-

Команды Linux.

Приложение B: арифметика с фиксированной точкой

Цель: использовать Fixed-Point Tool для преобразования вашего проекта программируемой логики в арифметику с фиксированной точкой.

-

Нормировка и наследование типов данных в fixed-point;

-

Рабочий процесс Fixed-Point Designer;

-

Fixed-Point Advisor;

-

Fixed-Point Tool;

-

Интерфейс командной строки.

MATLAB

MATLAB MATLAB для профессионалов (MLBE)

MATLAB для профессионалов (MLBE) «ИЦ «Бреслер» сократил на 50% сроки разработки терминала релейной защиты «ТОР 100-ЗЗН» при помощи MATLAB и Simulink

«ИЦ «Бреслер» сократил на 50% сроки разработки терминала релейной защиты «ТОР 100-ЗЗН» при помощи MATLAB и Simulink