HDL Verifier

HDL Verifier автоматически генерирует тестовые сценарии для верификации Verilog и VHDL модулей. Используйте MATLAB или Simulink для разработки и симуляции проекта, а затем технологию FPGA In the Loop для верификации его работы на реальной аппаратной платформе. Технология FPGA In The Loop поддерживается Xilinx, Microsemi, Intel.

HDL Verifier позволяет использовать разработанные в MATLAB и Simulink модели для автоматической генерации тестовых сценариев для таких симуляторов, как Cadence, Mentor Graphics, Synopsys. Синтезированные таким образом тесты удовлетворяют требованиям методики универсальной верификации UVM.

Верификация и поиск ошибок

Встраивайте поведенческие модели разработанных вами HDL-моделей в опорные проекты и эталонные модели Simulink, для проверки работоспособности и соответствия заданным стандартам. HDL Verifier поддерживает интеграцию с такими HDL-симуляторами, как Cadence Incisive & Xcelium, Mentor Graphics Modelsim & Questa, Xilinx Vivado Simulator.

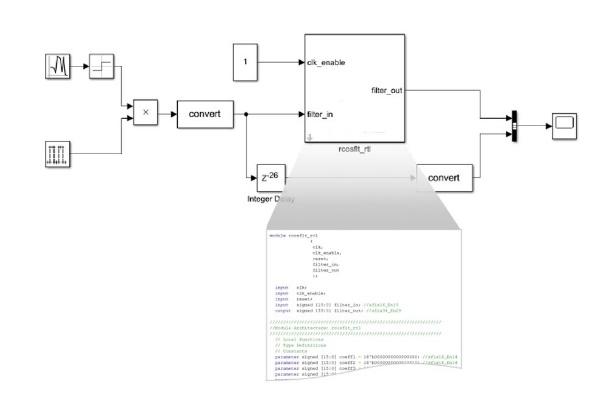

Интеграция с существующим HDL-кодом

Интегрируйте разработанные ранее HDL-модули в модели Simulink и алгоритмы MATLAB для проведения моделирования и симуляции на системном уровне. Используйте специализированную утилиту с графическим интерфейсом для автоматизированной интеграции Verilog или VHDL-кода, а также подключения к HDL-симуляторам от Mentor Graphics или Cadence.

Анализ степени покрытия HDL-кода тестами

Проектируйте и анализируйте тестовые сценарии в Simulink с применением утилит анализа покрытия и интерактивными дебагерами от Mentor Graphics или Cadence.

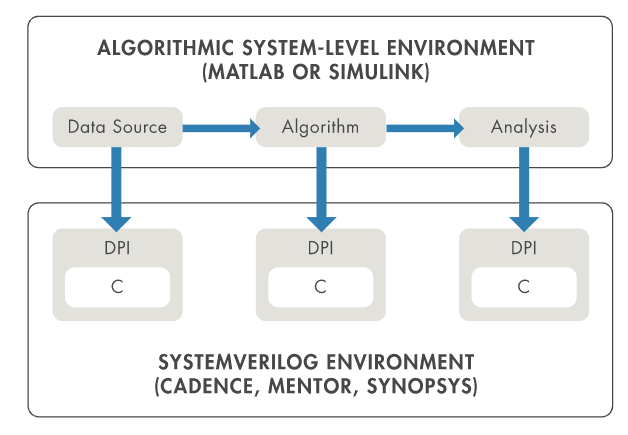

Генерация System Verilog DPI

Экспортируйте алгоритмы MATLAB или модели Simulink в среды верификации ASIC и FPGA разработок, включая Synopsys VCS, Cadence Incisive or Xcelium, Mentor Graphics Modelsim & Questa.

Экспорт компонентов

Генерируйте System Verilog DPI компоненты из функций MATLAB и блоков Simulink в поведенческие модели сред функциональный верификации.

Поддержка UVM

Генерируйте тестовые последовательности и сценарии из MATLAB функций и Simulink моделей согласно Universal Verification Methodology.

Конструкции System Verilog

Генерируйте разборчивые синтаксические конструкции System Verilog из моделей Simulink. Используйте полученные тесты для верификации работы алгоритма вне среды MATLAB Simulink или для верификации работы опытных образцов.

Верификация алгоритмов на целевой платформе

Отлаживайте и тестируйте алгоритмы на отладочных FPGA или опытных образцах, подключенных к MATLAB или Simulink.

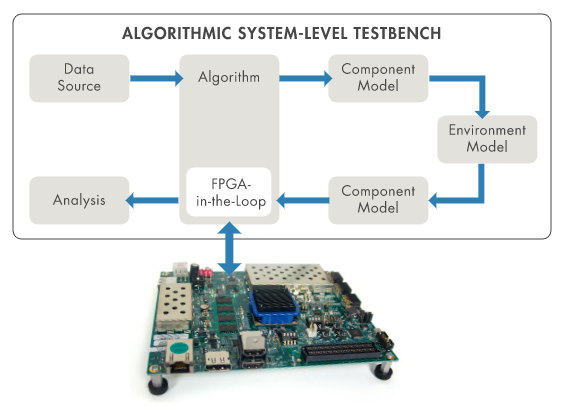

Тестирование FPGA In the Loop

Тестируйте работающие на реальном железе алгоритмы, используя тестовое окружение MATLAB или Simulink. Подключайте платы с ПЛИС XILINX, Intel, Microsemi к компьютеру с MATLAB при помощи Ethernet, Jtag, PCIe.

Захват данных с FPGA

Захватывайте потоки данных от алгоритмов, выполняющихся на ПЛИС, и автоматически загружайте их в MATLAB для визуализации и анализа. Анализируйте прохождение сигналов через разработанный алгоритм и верифицируйте его работу.

Доступ к памяти и внутренним ресурсам ПЛИС

Получите доступ к внутренним ресурсам FPGA через Ethernet/ Jtag /PCIe путем встраивания IP-ядра от MathWorks в проект ПЛИС. Тестируйте алгоритмы на ПЛИС, читая и записывая данные в AXI регистры и передавая большие объемы данных или изображения.

Интеграция с HDL-coder

Автоматизируйте процессы генерации кода и его верификации путем совместного использования инструментов HDL coder и HDL verifier.

Автоматизация совместной HDL-симуляции

Подключите автоматическую верификацию MHDL или Verilog кода в рабочий процесс.

Автоматизация тестирования FPGA прототипов

Проводите верификацию оборудования в среде MATLAB Simulink при помощи генерации конфигурационных файлов для ПЛИС Xilinx, Intel, Microsemi. Добавляйте тестовые точки и ядра для сбора и анализа данных.

Генерация System Verilog DPI тестовых сценариев

Производите синтез тестовых сценариев параллельно с генерацией HDL-кода. Верифицируйте сгенерированный HDL-код при помощи Synopsys, Cadence, Mentor Graphics симуляторов с использованием синтезированных сценариев.

Генерация TLM-2.0

Генерируйте IEEE 1666 SystemC TLM 2.0 совместимые модели уровня транзакций из Simulink.

Виртуальные прототипы

Генерируйте виртуальные SystemC прототипы с TLM 2.0 интерфейсами для использования в симуляторах виртуальных платформ.

Поддержка IP-XACT

Адаптируйте TLM интерфейсы сгенерированных компонентов, импортируя IP-XACT XML файлы. Используйте TLM генератор для формирования IP-XACT файлов для организации взаимодействия TLM компонентов и Simulink.

Новые возможности

- Захват данных и доступ к внутренним ресурсам ПЛИС

- MATLAB AXI master блок, для подключения к AXI шине через Ethernet

- MATLAB AXI master блок для подключения к AXI шине через PCI Express

- Поддержка различных FTDI USB-JTAG кабелей

- Генерация System Verilog DIPC компонентов

- Генерация System Verilog конструкций из окружения Simulink

Документация

Документация

Верификация и совместная симуляция

Верификация и совместная симуляция Опыт Harris corporation в применении HDL Verifier для ускорения процесса верификации

Опыт Harris corporation в применении HDL Verifier для ускорения процесса верификации

Улучшение RTL верификации при помощи интеграции с MATLAB

Улучшение RTL верификации при помощи интеграции с MATLAB

Генерация HDL описания для ПЛИС (SLHL)

Генерация HDL описания для ПЛИС (SLHL)