Stateflow

Рекомендуем библиотеку «Конечные автоматы» – это отечественная альтернатива продукту StateFlow, доступная в Engee, российской платформе для разработки сложных технических систем с применением методологии модельно-ориентированного проектирования.

Библиотека «Конечные автоматы» позволяет моделировать логику принятия решений с использованием графов переходов и машин состояний.

В редакторе конечных автоматов в Engee есть всё то, что нам нравится в StateFlow:

простота, наглядность и удобство;

богатые функциональные возможности для моделирования и отладки сложных масштабируемых систем.

Конечные автоматы

Модели с конечными автоматами поддерживают автоматическую генерацию встраиваемого кода.

Конечные автоматы в Engee позволяют комбинировать графы переходов и машины состояний, поддерживают иерархические состояния неограниченной вложенности, параллельные состояния и суперпереходы.

Для моделирования сложных сценариев можно использовать группы операторов внутри состояний, операторы темпоральной логики, индикаторы изменений и многое другое.

Всё то, к чему мы привыкли в StateFlow, доступно в библиотеке «Конечные автоматы» Engee. Это зрелый инструмент, позволяющий уже сейчас решать реальные инженерные задачи.

Примеры таких решений размещены в Сообществе Engee:

Для изучения возможностей библиотеки можно пройти учебный курс «Конечные автоматы».

Почему именно Engee

Почему мы рекомендуем именно Engee:

Единая среда для технических расчетов и динамического моделирования с помощью привычных блок-схем.

Облачная клиент-серверная архитектура.

Обширная быстро развивающаяся библиотека блоков.

Engee применяется для математики, машинного обучения, ИИ, систем управления, физического моделирования, цифровой обработки сигналов (ЦОС), радиокоммуникаций, РЛС, моделирования энергетики и т. д.

Подробная документация на русском языке.

Живое Сообщество с сотнями готовых примеров. Бесплатные учебные онлайн-курсы.

Ранее созданные скрипты MATLAB легко запустить в Engee и продолжить работу над ними.

После регистрации в Engee автоматически выдаётся бесплатная лицензия.

Общая информация о Stateflow

Stateflow предоставляет графический язык, который включает диаграммы переходов состояний, блок-схемы, таблицы переходов состояний и таблицы истинности. Вы можете использовать Stateflow, чтобы описать, как алгоритмы MATLAB и модели Simulink реагируют на входные сигналы, события и условия на основе времени.

Stateflow позволяет проектировать и разрабатывать диспетчерское управление, планирование задач, управление отказами, протоколы связи, пользовательские интерфейсы и гибридные системы.

С помощью Stateflow создается комбинаторная логика и логика принятия решений, которые можно смоделировать как блок в модели Simulink или выполнить как объект в MATLAB. Графическая анимация позволяет анализировать и отлаживать свою логику во время ее выполнения. Проверки во время редактирования и во время выполнения обеспечивают согласованность и полноту проектирования перед внедрением.

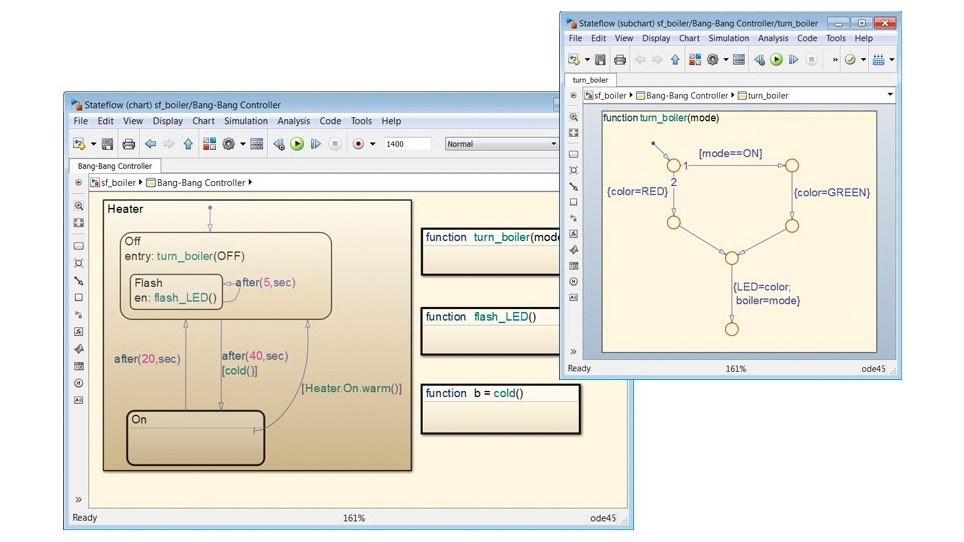

Разработка управляющей логики

Моделируйте системную логику, используя конечные автоматы, блок-схемы и таблицы истинности.

Графическое проектирование конечных автоматов

Конечные автоматы создаются графически, при помощи рисования состояний и соединений, связанных переходами. Также можно создавать функции, используя обозначения блок-схем, подсистемы Simulink, код MATLAB и таблицы истинности.

Разработка блок-схем

Блок-схемы создаются с помощью рисования переходов, которые соединены в узлах. Мастер шаблонов позволяет создавать часто используемые конструкции программирования. Такие блок-схемы можно использовать для разработки логики перехода между состояниями.

Разработка логики с помощью таблиц

Таблицы истинности позволяют моделировать логику в Simulink, когда результат зависит исключительно от текущего входа. Таблицы переходов состояний предоставляют структурированную среду для моделирования конечных автоматов в Simulink.

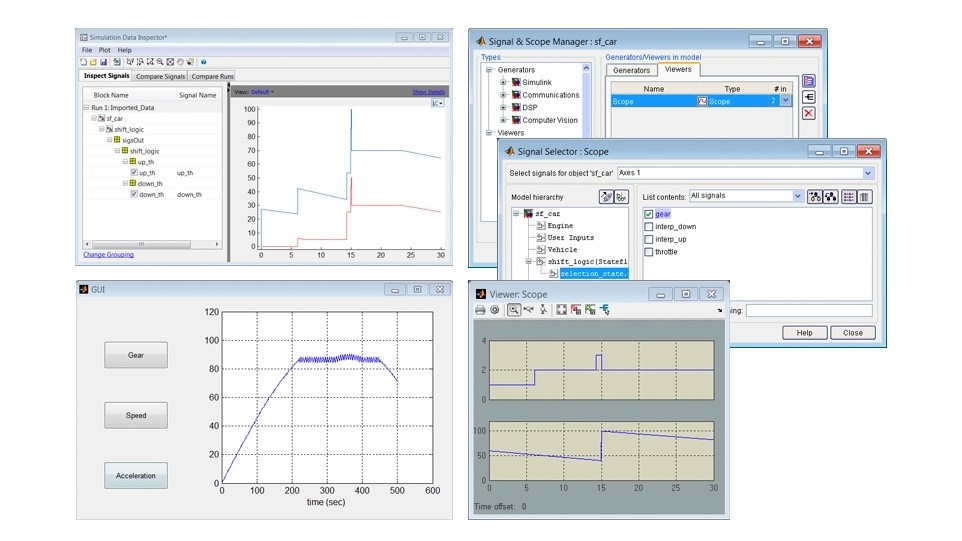

Выполнение и отладка диаграмм

Визуализация поведения системы для анализа и отладки.

Выполнение диаграмм Stateflow

Поведение системы визуализируется с помощью анимации диаграмм состояний для идентификации активных состояний и переходов.

Отладка диаграмм Stateflow

Средства отладки Stateflow позволяют детально описать выполнение диаграммы. Пользователь может установить точки останова, контролировать значения данных и выполнять различные функции на диаграммах состояний.

Разработка переиспользуемой логики для приложений MATLAB

Объекты диаграмм Stateflow могут быть использованы для разработки логики для приложений, созданных в MATLAB. Конечные автоматы и темпоральная логика используются для широкого спектра приложений, включая тестирование и измерения, автономные системы, обработку сигналов и связь.

Переиспользуемые объекты диаграмм

Stateflow позволяет создавать автономные диаграммы, которые используют все возможности языка MATLAB в действиях состояний и переходов. Эти диаграммы, в качестве объектов MATLAB, затем используются в пользовательских приложениях, которые требуют применения конечных автоматов и темпоральной логики.

Конечные автоматы и темпоральная логика

Применение Stateflow позволяет ускорить разработку приложений MATLAB за счет моделирования конечных автоматов и темпоральной логики в графическом виде, которые трудно реализовать в текстовом виде.

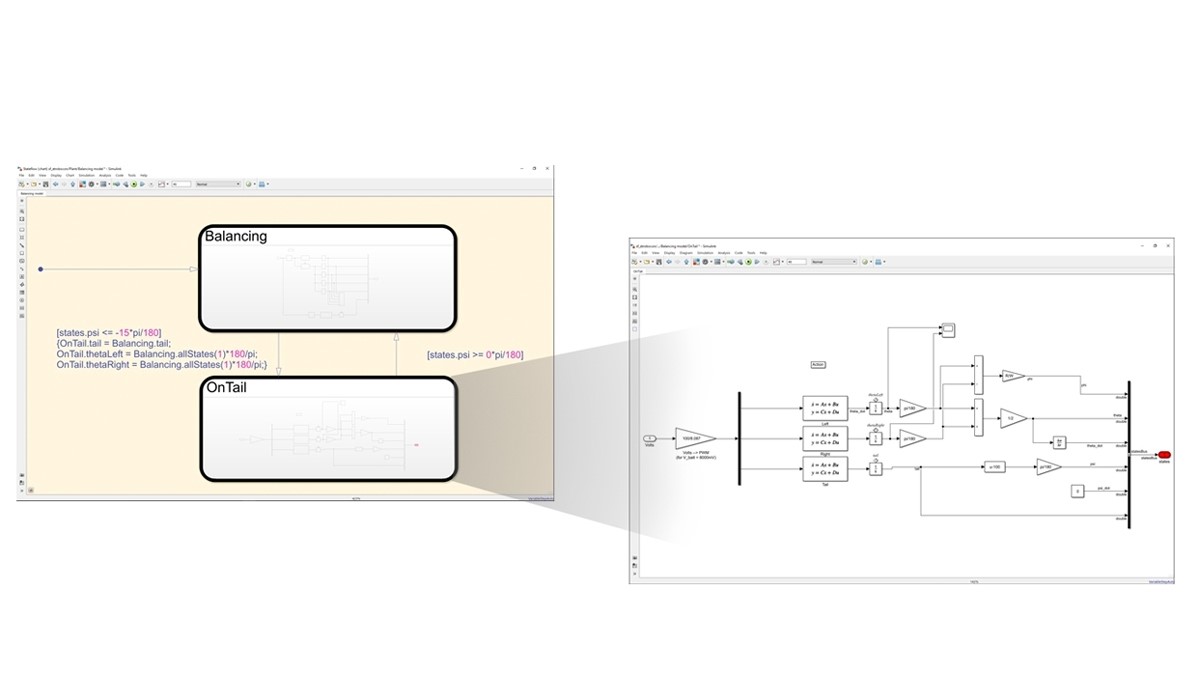

Планирование исполнения алгоритмов Simulink

Планирование вызовов алгоритмов, смоделированных в Simulink.

Периодическое и непрерывное планирование

Stateflow позволяет моделировать условную, основанную на событиях и основанную на времени логику для периодического или непрерывного вызова алгоритмов Simulink. С помощью Stateflow можно организовать выполнение компонентов, чтобы имитировать планирование вашей среды в реальном времени.

Временные операторы

С помощью Stateflow моделируются операторы, основанные на событиях или времени, которые задают логику перехода состояний на основе счетчиков событий, прошедшего времени и незашумленных сигналов без необходимости создавать и поддерживать свои собственные таймеры и счетчики.

Валидация проекта и генерация исходного кода

Диаграммы Stateflow проверяются на соответствие требованиям. Исходный код генерируется из диаграмм Stateflow для реализации во встраиваемых системах.

Валидация проекта

Stateflow используется с другими продуктами Simulink для проверки соответствия проекта требованиям.

- Требования связываются напрямую с объектами Stateflow, используя функцию перетаскивания в Simulink Requirements

- Статический анализ диаграмм на соответствие стандартам, с помощью Simulink Check

- Сбор покрытия моделей и кода с помощью Simulink Coverage

- Обнаружение ошибок проектирования и создание тестовых векторов с помощью Simulink Design Verifier

- Разработка, управление и выполнение тестов с помощью Simulink Test

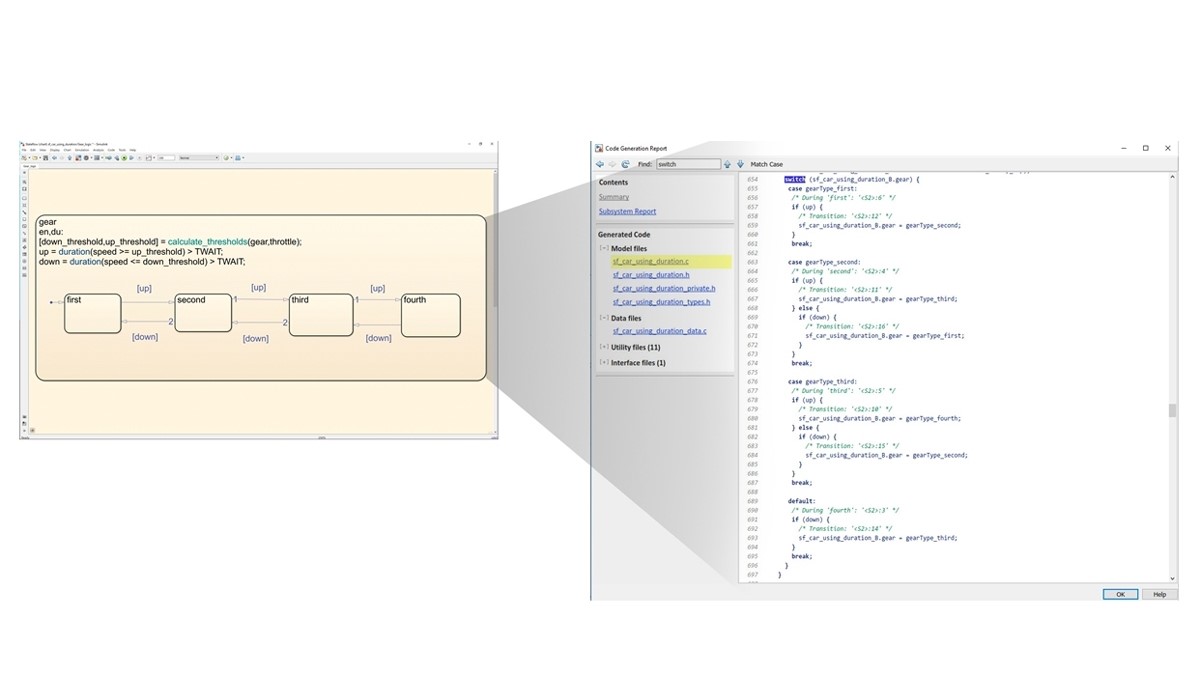

Генерация исходного кода

Исходный код генерируется из диаграмм Stateflow для реализации логики в встроенных системах.

- C/C++ код генерируется из моделей Simulink и Stateflow с помощью Embedded Coder

- VHDL и Verilog генерируются для FPGA и ASIC с помощью HDL Coder

- Structured Text для ПЛК и ПКК генерируется с помощью Simulink PLC Coder

Документация

Документация

Представление режимов работы в виде состояний

Представление режимов работы в виде состояний Таблицы переходов между состояниями (англ.)

Таблицы переходов между состояниями (англ.)

Конструкторы ФГУП ГНПРКЦ «ЦСКБ-Прогресс» моделируют ракеты в среде MATLAB

Конструкторы ФГУП ГНПРКЦ «ЦСКБ-Прогресс» моделируют ракеты в среде MATLAB