HDL Coder

Рекомендуем Вам перейти на Engee – Российскую платформу математических вычислений и динамического моделирования.

Генерируйте VHDL и Verilog код для ПЛИС и ASIC платформ.

HDL Coder формирует портируемый на платформы различных производителей Verilog и VHDL код из функций MATLAB, моделей Simulink и диаграмм Stateflow. Полученный код может быть использован для программирования FPGA или прототипирования заказных микросхем ASIC.

HDL Coder предоставляет интерфейс для управления и автоматизации рабочего процесса для FPGA таких производителей, как Xilinx, Microsemi, Intel. Вы можете контролировать архитектурные решения в ходе проектирования и синтеза HDL-проекта, выявлять и оптимизировать критические пути распространения сигнала, а также проводить предварительную оценку ресурсоемкости алгоритма. HDL Coder позволяет достичь взаимно однозначного соответствия между моделью Simulink и сгенерированным VHLD или Verilog кодом, кроме того присутствует функция верификации проектов с высокой плотностью размещения на кристалле согласно стандарту DO-254.

Основные характеристики HDL Coder

Основные возможности

- Генерация портируемого VHDL и Verilog кода, синтезируемого под ПЛИС большинства производителей

- Возможность генерации кода из MATLAB функций, системных объектов, Simulink блоков

- Проектирование конечных автоматов Мили и Мура, также различной логики управления при помощи Stateflow

- Автоматизированный процесс синтеза и программирования для ПЛИС Xilinx, Microsemi, Intel

- Возможность использовать различные стратегии проектирования (минерализация ресурсов, увеличение производительности и т.д.)

- Взаимно однозначное соответствие код-модель и модель-код, согласно стандарту DO-254

- Возможность встраивания в модель Simulink или MATLAB проект разработанного ранее HDL кода

Генерация HDL-кода

HDL Coder позволяет сгенерировать синтезируемый HDL код для ASIC и FPGA разработок в несколько шагов:

- Разработка проекта для целевой платформы с использованием различных комбинаций Simulink блоков, скриптов MATLAB, диаграмм Stateflow

- Оптимизация разработанной модели для достижения заданных характеристик синтезируемого кода

- Генерация HDL кода для различных применений с использованием встроенного планировщика рабочего процесса

- Верификация HDL кода с использованием HDL Verifier

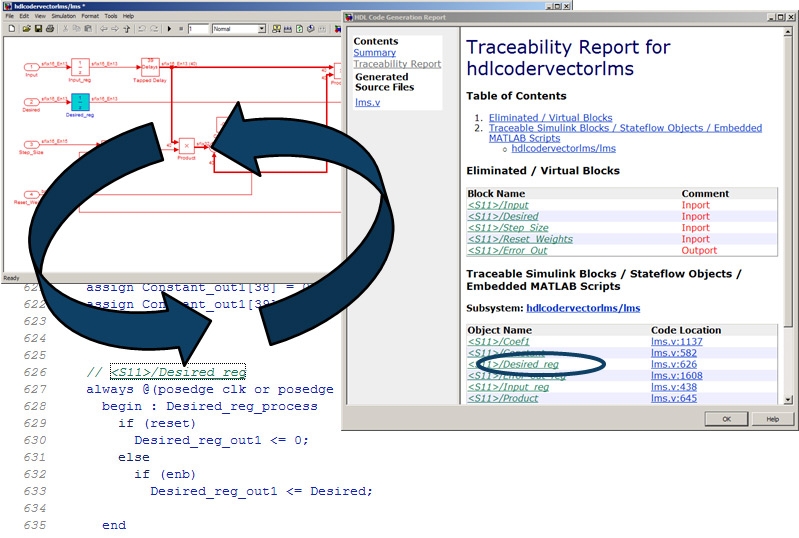

Документирование и анализ HDL кода

HDL Coder формирует читаемый Verilog и VHDL код, используя имена переменных и блоков из исходных MATLAB проектов или Simulink моделей. Во время генерации HDL кода вы можете создать отчет отслеживания, который представляет собой HTML файл и связывает HDL код с моделью Simulink или скриптом MATLAB, из которой он был синтезирован.

Для рабочих процессов, проводимых согласно стандарту DO-254, существует возможность совместить отчет отслеживания из HDL Coder с инструментарием отслеживания среды Simulink и получить предельно точный отчет о связи кода и модели.

HDL Coder имеет возможности генерации Verilog и VHDL кода в соответствии с популярными индустриальными требованиями к разработке, такими как RMM и STARC. В процессе генерации кода вы можете использовать Simulink Model Advisor для выявления не синтезируемых конструкций и производить оптимизацию и адаптацию модели под заданные стандартом требования.

Разработка проектов в среде MATLAB и Simulink для последующей генерации кода

При подготовке алгоритмов к переносу на целевую платформу важно преобразовать их для работы с битовыми потоками и шинами, а не блоками данных. Типовая последовательность этапов подготовки, следующая:

- управление потоками данных

- распараллеливание операций

- управление задержками в параллельных путях распространения

- сопоставление требуемых ресурсов с возможностями целевой платформы.

Применение блоков и системных объектов, оптимизированных для HDL-синтеза

HDL Coder поддерживает более 200 блоков Simulink, которые поддерживают специальные настройки и сценарии для синтеза HDL и трассировки на кристалле. Кроме того, для различных применений существуют специализированные наборы блоков, включая:

- Блоки и системные объекты управления памятью (RAM, ROM, FIFO)

- Блоки для сверхскоростной обработки сигналов (Gigasample-per-second (GSPS) processing) в DSP System Toolbox

- Блоки, реализующие алгоритмы обработки видеопотока и изображений в Vision HDL Toolbox

- LTE приемник и другие подсистемы в LTE HDL Toolbox

Данные с плавающей и фиксированной точкой

Для достижения заданных показателей по быстродействию и утилизации ресурсов FPGA или AISIC в большинстве случаев необходимо точно рассчитывать разрядность данных. В большинстве случаев перенос алгоритмов, разработанных в арифметике с плавающей точкой, в арифметику с фиксированной точкой представляет собой нетривиальную задачу, поскольку необходимо сохранить эквивалентность вычислений.

HDL Coder Native Floating Point позволяет генерировать синтезируемые VHDL и Verilog конструкции непосредственно из моделей, реализованных в рамках арифметики с плавающей точкой одинарной точности представления. Данный инструмент позволяет ускорить процесс прототипирования. В процессе перехода к вычислению алгоритма в арифметике с фиксированной точкой вы можете локализовать операции, требующие реализации с применением Native Floating Point, что позволит повысить производительность и сократить количество используемых ресурсов. Данное решение нашло свое применение в задачах реализации алгоритмов требующих высокой точности вычислений и большого динамического диапазона.

Fixed-Point Designer позволяет автоматизировать и контролирует процесс перевода алгоритмов в арифметику с фиксированной точкой. Данный инструмент использует результаты симуляции для определения необходимой длины слова на каждом из этапов вычислений. Результаты анализа могут быть использованы в чистом виде для реализации алгоритма или же инженер может внести корректировки, полагаясь на свой опыт.

Руководство по быстрому старту

Для начала адаптации вашего алгоритма к генерации из него HDL кода необходимо ознакомиться со Справочным руководством по данному инструменту.

Если у вас недостаточно опыта в сфере разработки на базе FPGA, то вы можете пройти курс “Цифровая обработка сигналов на ПЛИС”, который направлен на изучение основ реализации алгоритмов ЦОС. Кроме того, вы можете выбрать один из нескольких вариантов сотрудничества с ЦИТМ Экспонента от выполнения проекта под ключ до внедрения нашего инженера в вашу команду для обмена опытом и передачи экспертизы в ходе выполнения проекта.

Оптимизация HDL кода

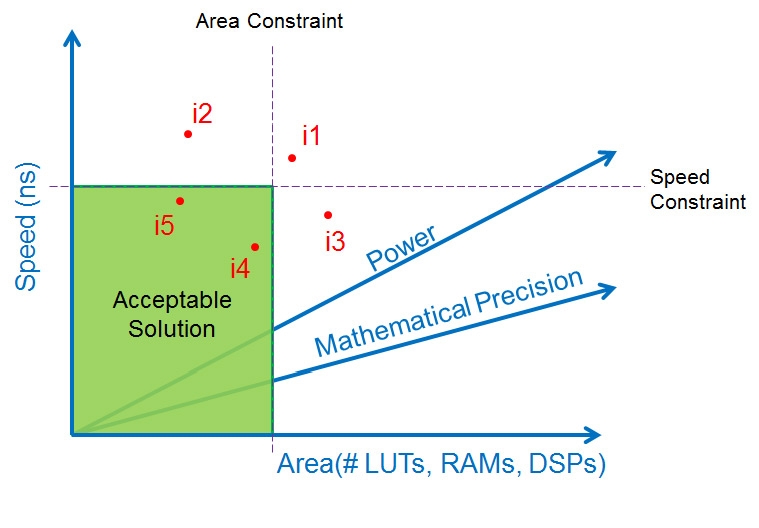

HDL кодер может существенно помочь в процессе оптимизации кода как для изготовления прототипа, так и для выпуска серийного образца. Параметры оптимизации могут как устанавливаться средой автоматически, так и быть заданы инженером. Для достижения максимальной тактовой частоты работы проекта HDL Coder может устанавливать ряды D-триггеров для устранения гонок сигналов в параллельных линиях. В задачах минимизации энергопотребления и занимаемых алгоритмом ресурсов кристалла HDL Coder может преобразовывать параллельные структуры и вычисления в последовательные, а также использовать одни и те же ресурсы для выполнения различных операций. Большинство из готовых к синтезу блоков Simulink, например, фильтры и математические операции обладают широким набором настроек для достижения оптимальных результатов синтеза.

Проектирование на архитектурном уровне позволяет более отчетливо видеть взаимосвязь между скоростью работы проекта и занимаемыми ресурсами при реализации таких операций, как обработка векторов данных, изменение частоты дискретизации сигнала, а также позволяет разделить проект на составляющие части, к которым предъявляются различные требования к синтезу и быстродействию.

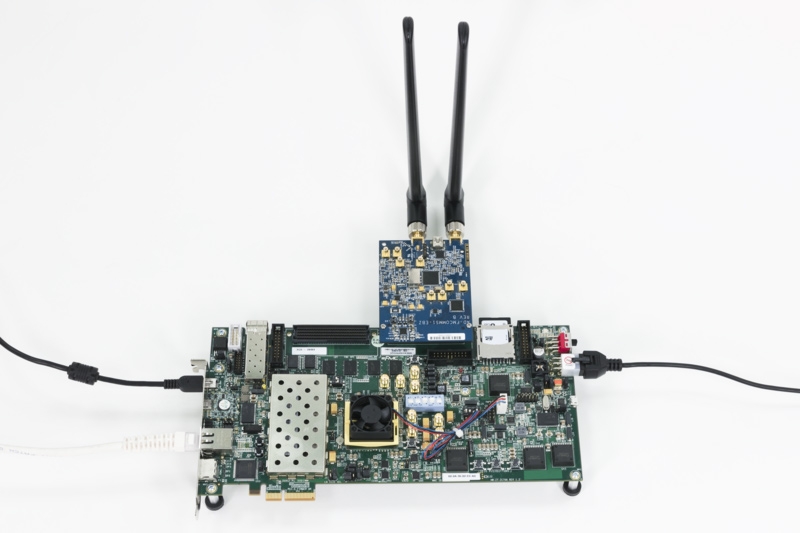

Быстрое прототипирование алгоритмов на FPGA

Инженеры ведущих мировых компаний часто применяют HDL Coder для построения прототипов с целью исследования работы алгоритмов в реальных условиях, а также оценки занимаемых требуемых ресурсов ПЛИС и тактовых частот. Перенос моделей на реальные аппаратные платформы требует поддержки высокоскоростных интерфейсов. HDL Coder поддерживает синтез блоков, позволяющих встроить разработанный алгоритм с применением наиболее распространённых шин, включая AXI.

Симуляция в реальном времени при помощи Simulink Real-Time и машины реального времени РИТМ

Для осуществления быстрого прототипировния алгоритмов управления, компьютерного зрения, сложных процессов с применением технологии оборудование в петле (HIL). Машина реального времени РИТМ с высокопроизводительными блоками ввода-вывода и минимальной задержкой позволяет организовать процесс полунатурного моделирования и верификации прототипов. Используя утилиту для управления процессом синтеза конфигурационного файла для FPGA, вы можете автоматически проектировать интерфейсы ввода-вывода для интеграции разработанного алгоритма.

Применение встроенных возможностей фиксации данных эксперимента, управления воздействием и анализа работы устройства с использованием машин реального времени ускоряют процесс поиска ошибок и сокращают количество итераций тестирования.

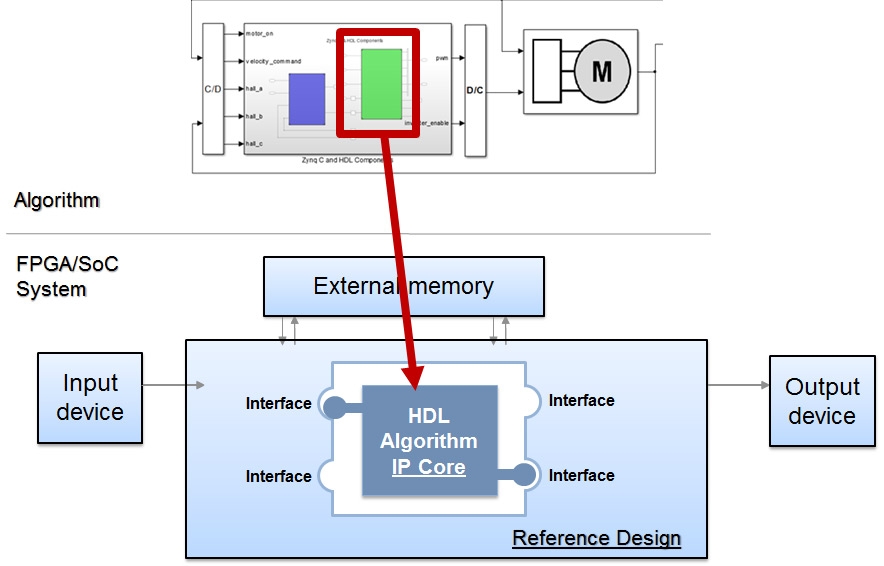

Переход к серийному производству

HDL Coder предоставляет широкий набор опций, предназначенных для проектирования интерфейсов ввода-вывода, что необходимо при переносе алгоритма с отладочной платы на целевую платформу. Кроме того, при реализации систем на кристалле HDL Coder позволяет создавать интерфейсы для взаимодействия с процессорным ядром.

При разработке сложных систем существует возможность создавать собственные IP-ядра и после проведения верификации вносить их в библиотеку блоков с целью повторного использования. Данные IP-ядра можно проектировать с возможностью подключения как с использованием стандартных (AXI и т.д.), так и пользовательских интерфейсов.

Проекты, реализованные при помощи HDL Coder:

Верификация HDL кода

HDL Coder позволяет синтезировать тестовые сценарии для верификации HDL проектов. Кроме того, вы можете внести в синтезированный сценарий изменения для проверки устойчивости разработанного проекта к различным внештатным ситуациям и сбоям. Помимо прочего существует возможность разработки скриптов для автоматизации процесса запуска HDL симулятора и выполнения тестов над сгенерированным модулем.

Совместное использование HDL Coder и HDL Verifier позволяет сгенерировать два вида тестовых сценариев:

- Совместную симуляцию модели Simulink с интегрированной поведенческой моделью разработанного модуля, путем организации обмена данными со следующими специализированным HDL-симуляторами: Cadence, Incisive, Modelsim, Questa.

- FPGA in The Loop (ПЛИС в петле) – тестовый сценарий в котором целевой модуль работает на ПЛИС и обменивается данными с моделью Simulink, которая формирует и обрабатывает тестовые воздействия.

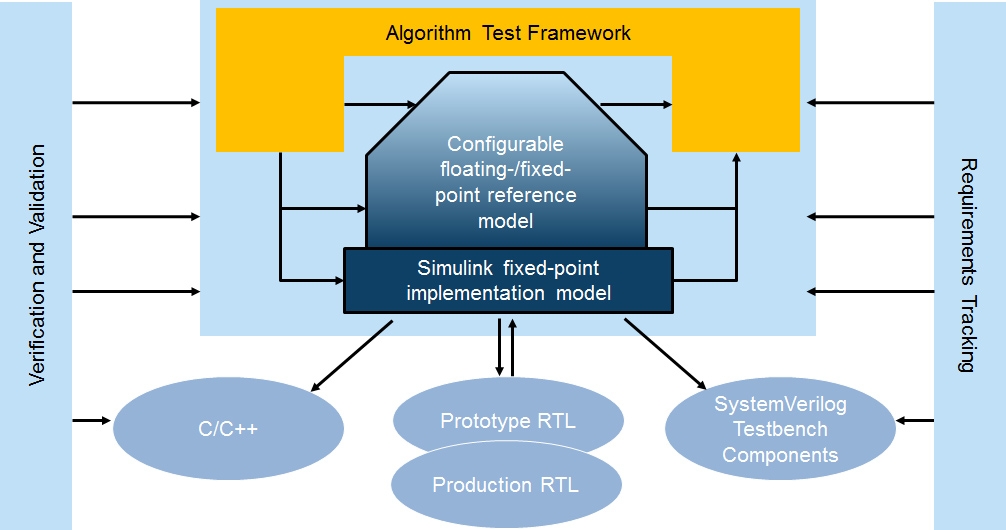

Автоматическая генерация HDL кода в рамках концепции модельно-ориентированного проектирования

Концепция модельно-ориентированного проектирования соединяет воедино разработку технического задания, разработку архитектуры, реализацию на целевой платформе и тестирование. Данный подход позволяет улучшить взаимодействие специалистов различного профиля между собой. В процессе проектирования модель разделяется на исполняемую часть и тестовую обвязку, которую можно использовать повторно на этапе верификации HDL кода или испытаний прототипа. В процессе разработки модель может постоянно совершенствоваться и наполняться деталями в соответствии с ее аппаратной реализацией, например, перевод вычислений в арифметику с фиксированной точкой, причем на каждой итерации внесения изменений данный подход позволяет протестировать работоспособность системы в целом и ее соответствие заданным требованиям.

Документация

Документация

Блоки, поддерживаемые для генерации кода HDL

Блоки, поддерживаемые для генерации кода HDL Модель проектирования смешанных сигналов для автомобильных датчиков

Модель проектирования смешанных сигналов для автомобильных датчиков Ускорение разработки датчиков с помощью быстрого прототипирования и модельно-ориентированного проектирования

Ускорение разработки датчиков с помощью быстрого прототипирования и модельно-ориентированного проектирования

Сертификация и разработка систем повышенной надежности

Сертификация и разработка систем повышенной надежности Радио ГИГАБИТ - Разработка модема на ПЛИС для радиорелейной системы связи миллиметрового диапазона с использованием методологии модельно-ориентированного проектирования

Радио ГИГАБИТ - Разработка модема на ПЛИС для радиорелейной системы связи миллиметрового диапазона с использованием методологии модельно-ориентированного проектирования