Deep Learning HDL Toolbox

Deep Learning HDL Toolbox™ располагает всеми необходимыми инструментами и функционалом для прототипирования и реализации глубокого машинного обучения на ПЛИС и СнК. Предоставляет возможность использования уже готовых в Deep Learning HDL Toolbox™ проектов для решения самых разных задач глубокого обучения на отладочных стендах ПЛИС фирм Xilinx и Intel, а также систем на кристалле. Средства профилирования и оценки позволяют настраивать нейронную сеть, исследуя её характеристики, эффективность и аппаратную ресурсоёмкость конечной проектируемой системы.

Deep Learning HDL Toolbox позволяет вам настраивать процесс аппаратной имплементации вашей нейронной сети и формировать компактный синтезируемый Verilog и VHDL код для реализации его в ПЛИС (применительно с пакетами HDL Coder и Simulink).

Интерфейс глубокого обучения на ПЛИС

Создание прототипов и реализация нейронных сетей на ПЛИС для периферийного развертывания.

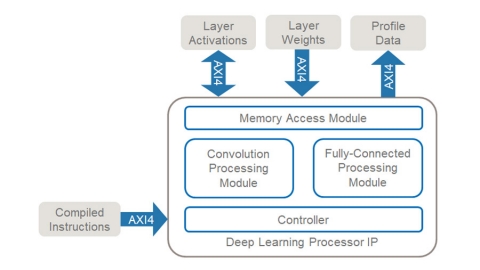

Программируемый процессор глубокого обучения (DLP)

Пакет содержит в себе процессор глубокого обучения (DLP) с функциями вычисления общей свёртки и управления полносвязными слоями нейронной сети. Данный процессор представляет собой набор логических выводов ПЛИС, разработанный в пакете Deep Learning Toolbox™. Интерфейсы памяти с высокой пропускной способностью ускоряют передачу данных о слоях и их весах в память.

Компиляция и внедрение проекта в ПЛИС

Скомпилируйте свою сеть глубокого обучения в набор инструкций, которые будет выполнять процессор глубокого обучения (DLP). Реализуйте на ПЛИС и выполняйте прогнозирование, фиксируя фактические показатели производительности.

Начните со встроенных в Deep Learning Toolbox проектов

Создайте прототип нейронной сети без написания кода для ПЛИС, используя доступные проекты для популярных отладочных стендов.

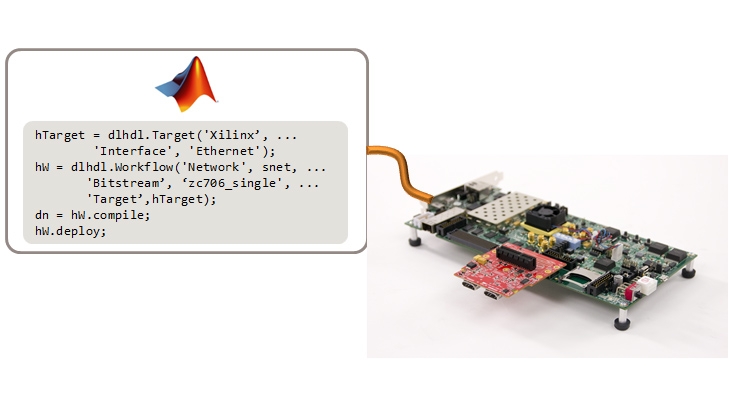

Интерфейс конфигурирования ПЛИС в MATLAB

Реализуйте процесс глубокого обучения ПЛИС из MATLAB.

Создание нейронной сети для внедрения в ПЛИС

Начните использовать Deep Learning Toolbox для проектирования, обучения и анализа вашей нейронной сети для таких задач, как обнаружение или классификация объектов. Вы также можете начать с импорта обученной сети или слоев из другого специализированного софта.

Внедрение вашей сети в ПЛИС

Если у вас есть обученная сеть, используйте команду deploy, чтобы запрограммировать ПЛИС с помощью ядра DLP по Ethernet или JTAG интерфейсу. Затем используйте команду сompile, чтобы сгенерировать набор инструкций для вашей обученной сети без перепрограммирования ПЛИС.

Выполнение логического ввода-вывода в ПЛИС как часть вашего MATLAB-приложения

Запустите ваше приложение в MATLAB, включая тестовый стенд, алгоритмы предварительной и постобработки, а также логический входы-выходы проекта в ПЛИС. Одиночная команда в MATLAB predit выполнит логический ввод в ПЛИС и возвратит результаты в рабочее пространство MATLAB.

Настройки нейронной сети

Настройте свою нейронную сеть в соответствии с требованиями конкретного приложения на целевом устройстве ПЛИС или СнК.

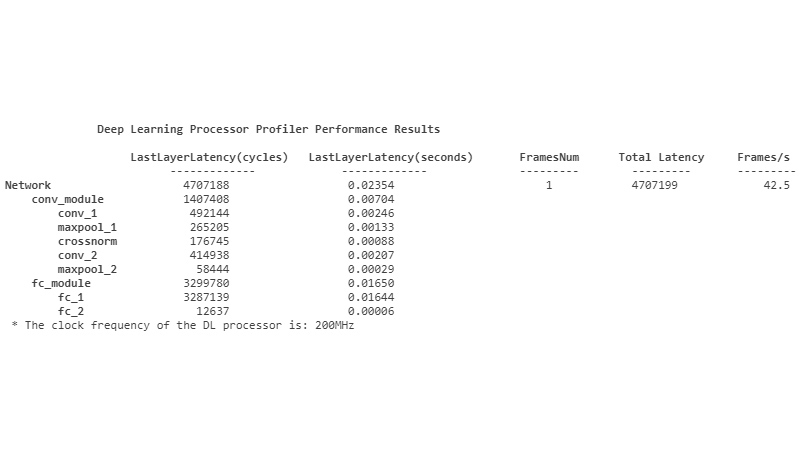

Профилирование интерфейса ПЛИС

Измеряйте задержку слоя сети при выполнении прогнозов на ПЛИС, чтобы найти "узкие места" в производительности.

Настройка дизайна сети

Используя параметры профиля, настройте конфигурацию сети с помощью Deep Learning Toolbox. Например, используйте Deep Network Designer для добавления слоев, удаления слоев или создания новых соединений.

Deep Learning и Квантование

Уменьшите расход ресурсов вашей нейронной сетью за счёт использования данных с фиксированной точкой. Анализируйте компромиссы между точностью и расходом ресурсов с помощью пакета поддержки библиотеки квантования моделей.

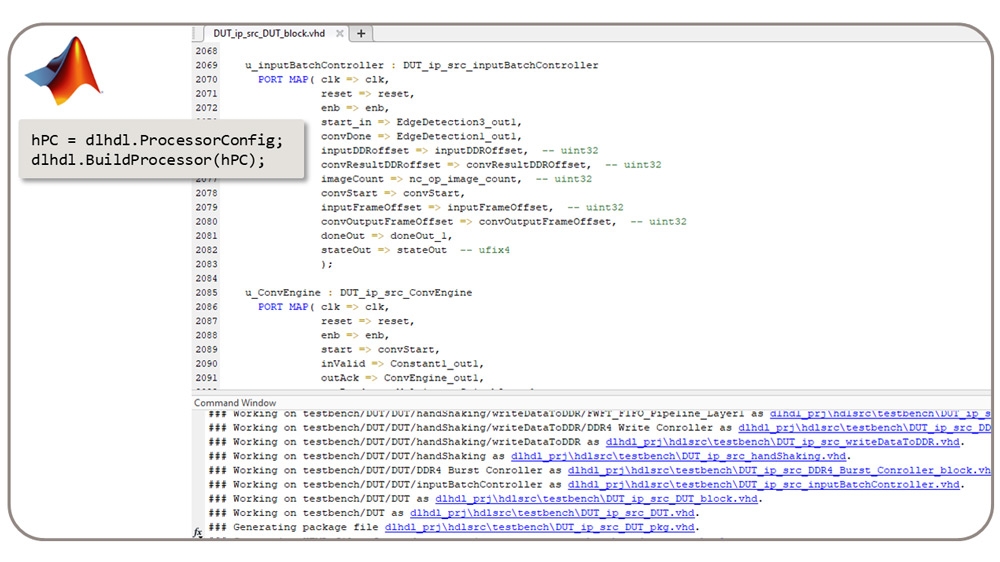

Сборка пользовательской RTL имплементации

Сборка пользовательской RTL имплементации процессора глубокого обучения (DLP) для ПЛИС, ИССН или СнК с HDL Coder.

Пользовательская конфигурация процессора глубокого обучения (DLP)

Укажите параметры аппаратной архитектуры для реализации процессора глубокого обучения, такие как количество параллельных потоков или максимальный размер слоя.

Генерация синтезируемого RTL проекта

Используйте HDL Coder для создания синтезируемого RTL проекта из процессора глубокого обучения (DLP) для использования в различных рабочих процессах и устройствах. Повторно используйте один и тот же процессор глубокого обучения для развертывания прототипов и создания конечных устройств.

Генерация IP-ядер для интеграции

Когда HDL Coder генерирует RTL проект из DLP, он также генерирует IP-ядро со стандартными интерфейсами AXI для интеграции в ваш эталонный дизайн СнК.

Архитектура DLP

Архитектура DLP ПЛИС Xilinx и СнК поддерживаемые Deep Learning HDL Toolbox

ПЛИС Xilinx и СнК поддерживаемые Deep Learning HDL Toolbox Используйте MATLAB для прототипирования систем глубокого обучения на ПЛИС Xilinx

Используйте MATLAB для прототипирования систем глубокого обучения на ПЛИС Xilinx