Simulink PLC Coder

Структурированные текстовые и лестничные диаграммы генерируются в формате PLCopen XML и других форматах файлов, поддерживаемых широко используемыми интегрированными средами разработки (IDE), включая 3S-Smart Software Solutions CODESYS, Rockwell Automation Studio 5000, Siemens TIA Portal и Omron Sysmac Studio.

В результате можно скомпилировать и развернуть приложение на многочисленных устройствах с программируемым логическим контроллером (PLC, ПЛК) и программируемым контроллером автоматизации (PAC, ПКА).

Simulink PLC Coder генерирует тестовые окружения, которые помогают вам проверить структурированные текстовые и лестничные диаграммы используя среды разработки для ПЛК и ПКА и инструменты симуляции. Он также предоставляет отчеты о генерации кода со статическими метриками кода и двунаправленной прослеживаемостью между моделью и кодом. Поддержка отраслевых стандартов доступна через IEC Certification Kit (для IEC 61508 и ISO 26262).

Запускайте где угодно

Генерация структурированного текста и лестничных диаграмм. Развертывание кода без лицензионных платежей.

Поддержка сторонних сред разработки

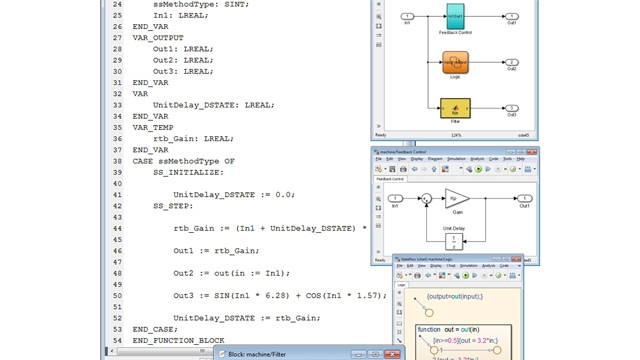

Simulink PLC Coder генерирует структурированный текст в различных форматах файлов, используемых сторонними IDE, включая Siemens STEP 7/TIA Portal, Rockwell Automation Studio 5000, 3S CODESYS и PLCopen XML. Simulink PLC Coder также генерирует лестничные диаграммы для Rockwell Automation Studio 5000, 3S CODESYS и PLCopen XML.

Генерация структурированного текста

Благодаря поддержке более 180 блоков Simulink, всех конструкций Stateflow и многих функций MATLAB, Simulink PLC Coder генерирует структурированный текст из моделей вашей системы управления, включающий петли обратной связи, логику режимов и состояний, а также математические алгоритмы.

Импорт и создание лестничных диаграмм

Импортируйте лестничные диаграммы Rockwell Automation Studio 5000 в Simulink для симуляции и верификации. Создавайте лестничные диаграммы из моделей Simulink для Studio 5000. Проверяйте созданные лестничные диаграммы путем создания и выполнения тестового стенда, работающего в эмуляторе из среды разработки.

Оптимизация кода, тестирование и проверка

Убедитесь, что сгенерированный код работает эффективно и правильно на PLC.

Оптимизация кода

Simulink PLC Coder применяет оптимизации для уменьшения объема памяти и увеличения скорости выполнения сгенерированного структурированного текста и лестничных диаграмм. Эти оптимизации включают устранение мертвого кода, свертывание выражений и повторное использование подсистем.

Комментирование, двунаправленная трассировка и документирование кода

Комментарии, пользовательские описания блоков и двунаправленные ссылки позволяют перемещаться между компонентами модели Simulink и сгенерированным кодом. Отчет о генерации кода объединяет всю информацию для проверки и отладки кода.

Тестирование и верификация кода

Создайте тестовое окружение для проверки результатов симуляции Simulink относительно результатов в ПЛК. Запустите HIL тестирование в режиме реального времени с помощью Simulink PLC Coder совместно с Simulink Coder, Simulink Real-Time и целевым компьютером РИТМ.

Документация

Документация Поддерживаемые среды разработки для генерации кода под ПЛК

Поддерживаемые среды разработки для генерации кода под ПЛК Основы работы с генератором кода (SLTG)

Основы работы с генератором кода (SLTG) Simulink

Simulink