Vision HDL Toolbox

Vision HDL Toolbox предоставляет алгоритмы для потоковой обработки видео и изображений для разработки систем видеоаналитики и видеонаблюдения работающих в реальном времени для развертывания систем на FPGA и ASIC. Инструмент поддерживает широкий набор интерфейсов, разрешений и частот кадров, включая HD видео разрешением 1920х1080p. В этом инструменте алгоритмы компьютерного зрения для обработки изображений и видео используют потоковую архитектуру и обрабатывают кадр попиксельно, и подходят для аппаратной реализации на FPGA и ASIC.

Из алгоритмов Vision HDL Toolbox генерируется читаемый и синтезируемый VHDL и Verilog код (совместно с HDL Coder). Сгенерированный HDL-код позволяет обрабатывать видео разрешением 1920х1080p и кадровой частотой 60 Гц в реальном времени.

Функции и алгоритмы инструмента доступны в виде системных объектов MATLAB и в виде Simulink блоков.

Примеры разработок

Ознакомьтесь с примерами разработок.

Примеры реализованных алгоритмов в Vision HDL

Начните изучение Vision HDL с примеров показывающих основные методы при разработке алгоритмов компьютерного зрения предназначенных для аппаратной реализации. Все алгоритмы, представленные в примерах, готовы к генерации Verilog и VHDL кода, с использованием HDL Coder.

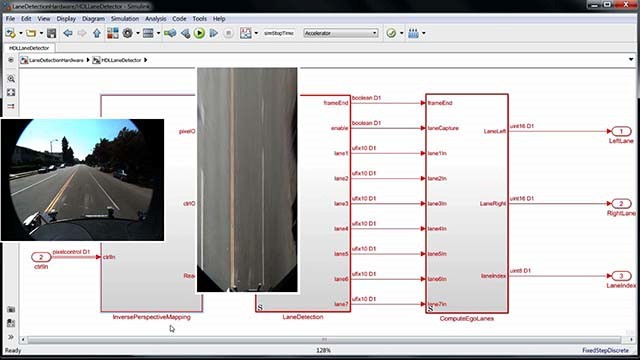

Автономное вождение

Начните строить свою систему автономного вождения с использованием проверенных на «железе» алгоритмов: обнаружения полосы движения, обнаружения выбоин и построения карты глубины по стереокамере.

Обнаружение признаков

Узнайте, как реализованы алгоритмы обнаружения признаков с потоковой архитектурой для разработки систем наблюдения, отслеживания объектов, промышленного контроля, и других приложений.

Обработка данных с камеры

Начните создавать свое собственное оборудование для обработки видео изображения используя примеры из документации: по удалению шума, гамма-коррекции и нахождению гистограммы.

IP блоки для обработки видео

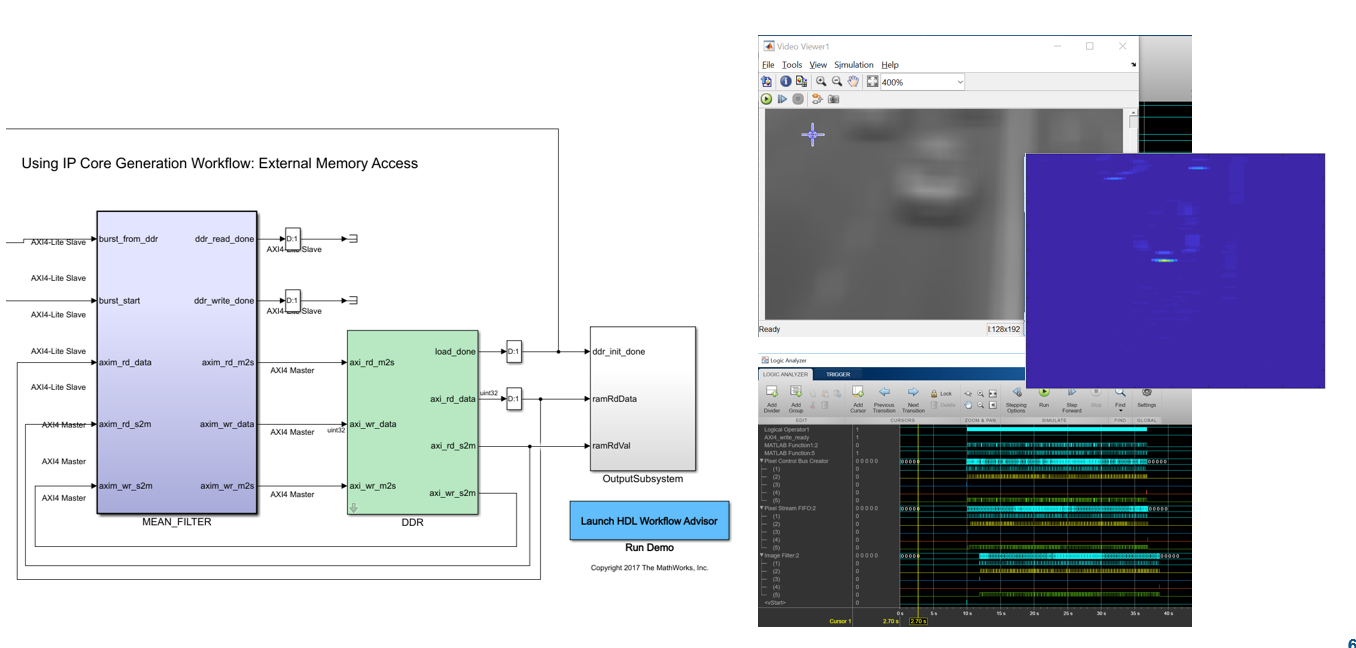

IP (Intellectual property) блоки в Vision HDL Toolbox предоставляют эффективные аппаратные реализации для вычислительно нагруженных алгоритмов, которые обычно создаются на аппаратном уровне. Это позволит вам ускорить процесс разработки подсистем обработки видео и изображений.

Аппаратное ускорение алгоритмов обработки видео и изображений

Моделируйте и создавайте эффективные аппаратные реализации алгоритмов обработки видео и изображений: предобработка, фильтрация, морфология и статистика. А после используйте HDL Coder для получения VHDL и Verilog кода из ваших алгоритмов.

Встроенные сигналы для управление данными

Используйте блоки из Vision HDL для генерации управляющих сигналов для управления потоковыми данными и генерации логических сигналов: сигналы области интереса (ROI), буфера строк и т.д. А после используйте HDL Coder для генерации VHDL и Verilog кода из алгоритма и использования этих же управляющих сигналов для контроля функционирования вашего алгоритма, но уже на FPGA.

Блоки для аппаратной реализации

Создайте свои собственные аппаратные блоки для управления данными с помощью библиотечных блоков: буферов строк, выбора области интереса, FIFO-буферов и выравнивателей сигналов для потоковых пиксельных данных и блоков для генерации управляющих сигналов.

Верификация на основе алгоритмов покадровой обработки

Подключите в модели алгоритм с покадровой обработки видео и на его основе эффективно проверяйте и верифицируйте ваш алгоритм с потоковой архитектурой.

Преобразование между кадром и потоком пикселей

Конвертируйте полнокадровое видео в поток пикселей с управляющими сигналами для обработки данных на «железе». После обработки данных на «железе» вы можете сконвертировать поток пикселей обратно в кадр для верификации и проверки алгоритма относительно эталонной модели алгоритма в MATLAB или в Simulink.

Примеры и шаблоны для верификации в MATLAB и Simulink

Изучите как использовать алгоритмы из Image Processing Toolbox и Computer Vision Toolbox, как их тестировать и верифицировать на вашем «железе».

HDL и FPGA косимуляция

Используйте HDL Verifier для верификации ваших алгоритмов совместно с HDL-симуляторами и для косимуляции алгоритмов на вашей отладочной плате с FPGA, совместно с эталонной моделью алгоритма в MATLAB или в Simulink.

Развертывайте алгоритмы на FPGA, ASIC и SoC

Простой перенос алгоритмов компьютерного зрения на FPGA для их прототипирования и тестирования в реальном времени на потоковом видео, и простое переиспользование моделей алгоритмов при запуске серийного производства.

Платформа для прототипирования алгоритмов с потоковым видео

Прототипируйте ваши алгоритмы обработки видео используя инструменты Computer Vision Toolbox, пакет поддержки Support Package for Xilinx Zynq совместно с HDL Coder и Embedded Coder для генерации кода из ваших алгоритмов в MATLAB и Simulink.

Запуск в серийное производство

Используйте HDL Coder для генерации высококачественного платформо независимого кода с AXI интерфейсами из ваших MATLAB и Simulink моделей и алгоритмов.

Документация

Документация

Реализация нейронной сети на ПЛИС

Реализация нейронной сети на ПЛИС Система «Видеодетектор огня»

Система «Видеодетектор огня»

Детектор линий разметки

Детектор линий разметки

Разработка алгоритмов обработки видео для Zynq

Разработка алгоритмов обработки видео для Zynq