Ускорение разработки программ ПЛИС с помощью инструментов MathWorks и Xilinx

Модельно-ориентированное проектирование (МОП) с помощью MATLAB/Simulink позволяет находить ошибки разработки на ранних этапах, ускоряя процесс проектирования за счет автоматизаций и повторного использования наработок. С помощью МОП затраты на разработку алгоритмов для ПЛИС сокращаются в разы, что подтверждается обилием «спасенных» проектов.

Модельно-ориентированное проектирование с автоматической генерацией HDL кода обеспечивает бесшовный процесс проектирования, включая перевод в арифметику с фиксированной запятой и конвейеризацию. Однако генератор HDL кода не поддерживает весь спектр блоков Simulink, в отличие от генератора встраиваемого Си кода.

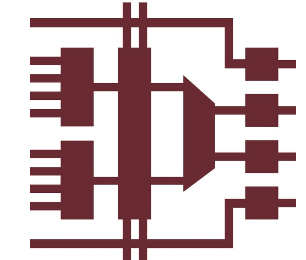

На данном вебинаре мы рассмотрим альтернативный подход, который включает генерацию Си кода из модели Simulink и последующее создание прошивки ПЛИС с использованием инструмента Xilinx Vivado HLS.

Xilinx Vivado HLS инструмент получения программ ПЛИС с помощью алгоритмических языков высокого уровня, в том числе Си кода. Программа на Си дополняется специальными директивами, которые описывают аппаратные свойства получаемой программы. Процесс разработки Xilinx Vivado HLS включает несколько этапов верификации, в которых сравнивается поведение исходного Си кода и полученного RTL кода.

Этот подход можно использоваться для быстрого прототипирования, ускорения симуляции сложных моделей и, при некотором усердии, получения прошивки производственного качества. Мы продемонстрируем эту технологию на нескольких наглядных примерах из области обработки изображений и ЦОС.

По ходу вебинара вы сможете задавать свои вопросы, которые могут повлиять на его содержание.

Сферы применения: ПЛИС и СнК