IP-ядро FFTex-IP

Данный продукт будет широко востребован в существующих и проектируемых системах радиосвязи.

Сферы применения:

- Базовые станции 3G/4G/LTE/5G NR.

IP-ядро используется для обработки сигналов в базовых станциях мобильной связи, обеспечивая высокую производительность и гибкость конфигурации.

Системы связи с OFDM-модуляцией.

IP-ядро идеально подходит для OFDM-модуляторов и демодуляторов, используемых в различных стандартах беспроводной связи.

Радиолокационные системы.

Для быстрой обработки отражённых сигналов и повышения точности детекции.

Спутниковая связь и навигация.

Обеспечение высокопроизводительной обработки сигналов для систем спутниковой связи и навигации, таких как GPS и ГЛОНАСС.

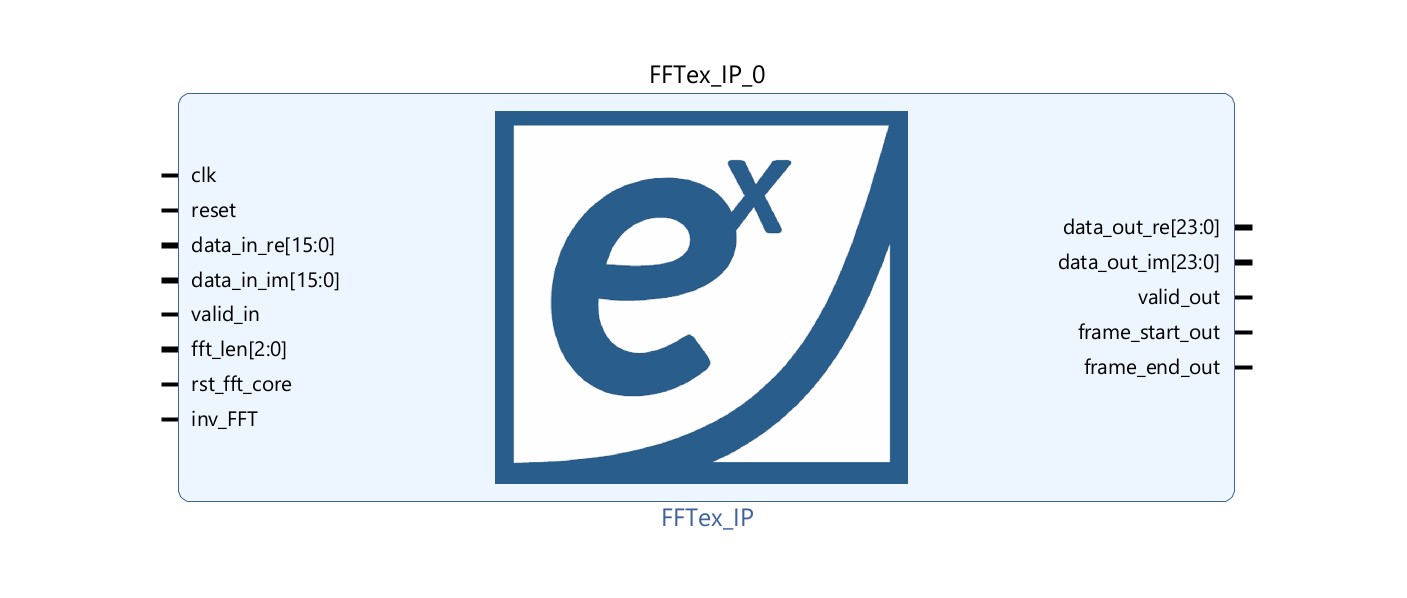

Технические характеристики FFTex-IP

Архитектура – Streaming Radix-4

Максимальная тактовая частота работы ядра – 270 МГц (Xilinx Zynq7100/Zynq7045/Kintex-7)

Максимальное значение длины БПФ – 2048

Минимальное значение длины БПФ – 128

Поддержка конфигурации количества ресурсных блоков для LTE (TS 36.212) 6, 15, 25, 50, 100

Используемые ресурсы:

LUT – 5822

DSP – 16

FF – 8553

RAMB36E1 – 10

Потоковая архитектура IP-ядра FFTex-IP Radix-4 имеет минимальную задержку обработки сигнала. Данная архитектура отличается от стандартного решения Radix-2, основанного на перегруппировке и разделении БПФ/ОБПФ. Архитектура

Radix-4 имеет log4(N) стадий, где N – длина БПФ. Каждая стадия содержит два примитива с единичной задержкой (SDF).

Опционально доступно округление и масштабирование на каждой операции типа «бабочка». IP-ядро FFTex-IP позволяет изменять тип преобразования с БПФ на ОБПФ и обратно без переконфигурации ядра.

Для тестирования и симуляции IP-ядра FFTex-IP возможна поставка завершённого тестового окружения реализованного с помощью языков описания Verilog/VHDL с привязкой к конкретному типу симулятора: Mentor Graphics ModelSim/Cadence Incisive/Xilinx Vivado Simulator.

Интеграция IP-ядер от ЦИТМ Экспонента в ваш проект

IP-ядро FFTex-IP от ЦИТМ «Экспонента» доступно для использования в составе FPGA и СБИС. Для специальных применений возможно использование указанного IP-ядра в составе специализированных СнК.

Интеграция IP-ядра FFTex-IP в текущие или будущие проекты возможна в соответствии с любыми требованиями и пожеланиями заказчика и производится силами инженеров ЦИТМ Экспонента.

Используйте в вашем проекте протестированные, оптимизированные, безопасные IP-ядра, а также техническую поддержку и помощь в настройке и интеграции этих решений от ЦИТМ Экспонента.

IP-ядра разработаны в России и могут быть использованы как с импортной, так и с отечественной электронной компонентной базой. Мы проконсультируем вас по выбору и внедрению IP-ядра в ваш проект и поможем довести работы до полного соответствия техническому заданию проекта.

Скачать datasheet по FFTex-IP

Скачать datasheet по FFTex-IP