Mixed-Signal Blockset

Mixed-Signal Blockset предоставляет модели компонентов и неидеальностей, инструменты анализа, а также тестбенчи для разработки и верификации интегральных схем (ИС) со смешанными сигналами.

Вы можете моделировать PLL, преобразователи данных и другие системы на разных уровнях абстракции и исследовать ряд архитектур ИС. Можно настраивать модели для включения таких неидеальностей, как шум, нелинейность и эффекты квантования, а также уточнить описание системы с помощью методологии "сверху вниз".

С помощью предоставляемых тестбенчей можно верифицировать производительность системы и повысить точность моделирования путем приближения измерительных характеристик или результатов симуляции на уровне схемы. Быстрая симуляция на системном уровне с помощью решателей Simulink с переменным шагом позволяет отлаживать реализацию и выявлять конструктивные недостатки перед моделированием ИС на транзисторном уровне.

С Mixed-Signal Blockset вы можете моделировать аналого-цифровые компоненты вместе со сложными алгоритмами цифровой обработки сигналов и логики управления. В результате как аналоговые, так и цифровые проектные группы могут работать с одной и той же исполняемой спецификацией.

Проектирование на системном уровне

Проектирование систем со смешанными сигналами с использованием моделей типовых архитектур. Задайте параметры модели, используя значения из спецификации. Следуйте методике «сверху вниз» и используйте модели белого ящика в качестве отправной точки для вашего проекта.

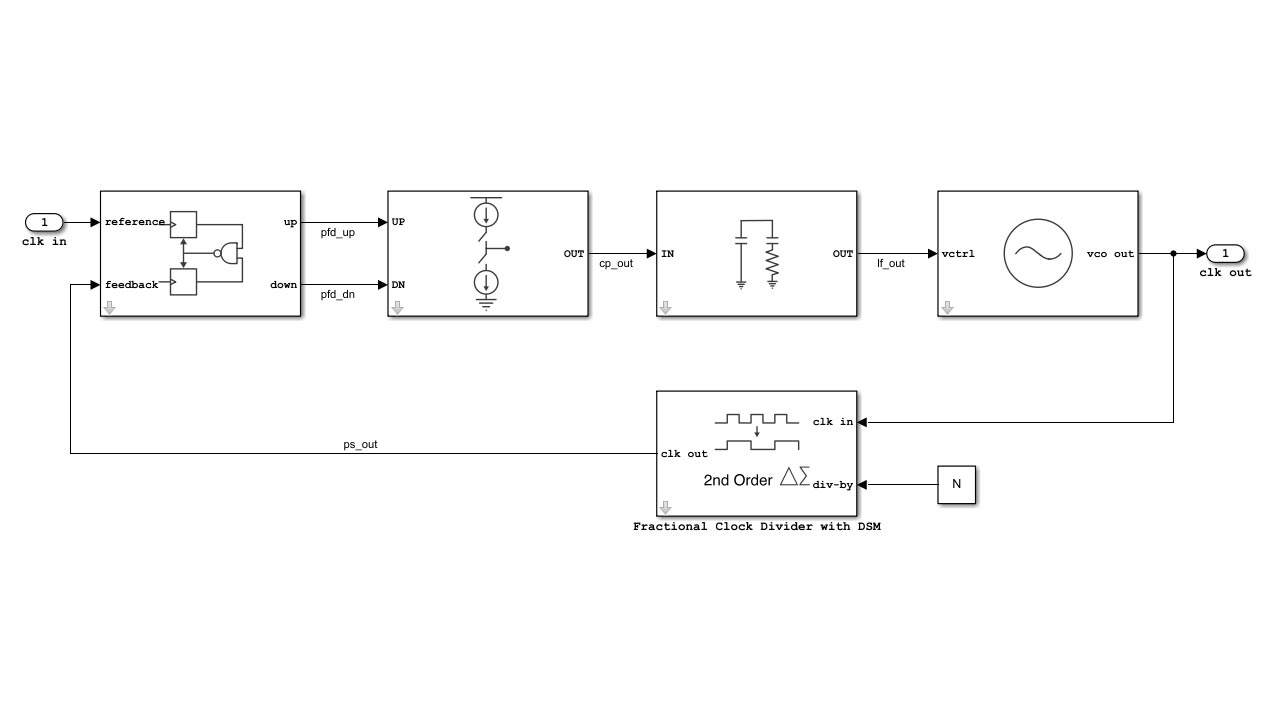

Разработка PLL

Проектирование и симуляция контуров фазовой автоподстройки частоты (ФАПЧ) на системном уровне. Типичные архитектуры включают в себя целочисленные-N ФАПЧ с одиночным или двойным предделителем и дробные-N ФАПЧ с аккумуляторами или дельта-сигма модуляторами. Верифицируйте и визуализируйте отклик разомкнутого и замкнутого контуров вашего проекта.

Разработка АЦП

Разработка и симуляция аналого-цифровых преобразователей данных (АЦП) на системном уровне, включая ошибки синхронизации и квантования. Типичные архитектуры включают АЦП прямого преобразования (flash) и регистр последовательного приближения (SAR).

Поведенческие модели со смешанными сигналами

Создавайте пользовательские системы со смешанными сигналами используя строительные блоки и включая типичные неидеальности.

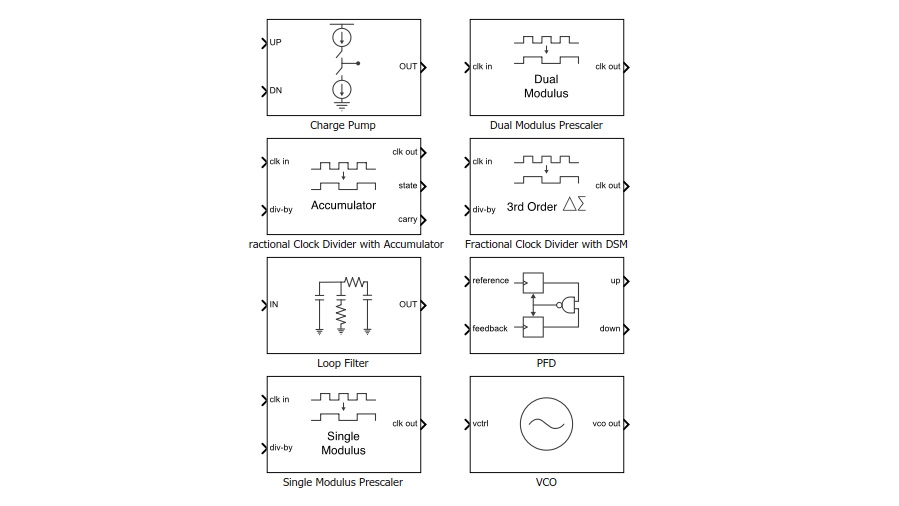

Библиотека строительных блоков

Создавайте собственные системы со смешанными сигналами, используя строительные блоки, такие как зарядовые насосы, петлевые фильтры, фазочастотные детекторы (PFD), генераторы, управляемые напряжением (VCO), делители тактовых импульсов и источники тактовых импульсов выборки. Вы можете уточнять аналоговые модели на более низком уровне абстракции с Simscape Electrical.

Моделирование неидеальностей

Моделируйте временные эффекты, фазовый шум, джиттер, утечку и другие неидеальности в вашей симуляции.

Временные неидеальности

Моделируйте время нарастания и спуска фронтов, конечные скорости нарастания и переменные временные задержки в ваших петлях обратной связи. С подобными эффектами синхронизации вы можете запускать симуляции для оценки стабильности и времени блокировки.

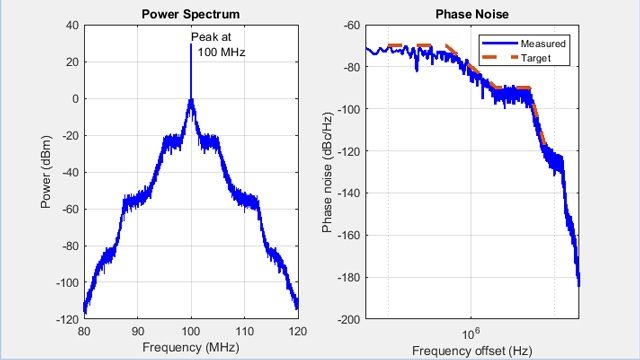

Фазовый шум и джиттер

Моделируйте джиттер в АЦП и указывайте произвольные профили фазового шума в частотной области для VCO и PLLs. Визуализируйте эффекты с помощью глазковой диаграммы.

Тестирование и верификация

Верифицируйте производительность ваших PLL и АЦП с помощью метрик конкретных приложений. Повторно используйте ваш тестбенч в сторонних инструментах проектирования ИС.

Тестбенчи

Измеряйте время блокировки, профиль фазового шума и рабочую частоту PLL, а также характеризуйте производительность ваших строительных блоков, таких как VCO, PFD и зарядовые насосы. Измеряйте характеристики переменного и постоянного токов, а также джиттер АЦП.

Интеграция со средами симуляции ИС

Повторно используйте системные модели со смешанными сигналами в выбранной среде проектирования ИС с помощью ко-симуляции или путем генерации модуля SystemVerilog с помощью HDL Verifier. Для цифровой части вашей системы вы можете генерировать синтезируемый HDL-код с помощью HDL Coder.

Новейшие функции

Знакомство с Mixed-Signal Blockset

Проектирование, моделирование и верификация аналоговых и смешанных систем.

Поведенческие модели белого ящика для PLL и АЦП

Проектирование и анализ систем со смешанными сигналами на основе типовых архитектур с использованием спецификации.

Строительные блоки

Проектирование пользовательских систем со смешанными сигналами по методике «сверху вниз».

Модели неидеальностей

Моделирование эффектов времени, фазового шума, джиттера, утечки и других.

Измерительные блоки и тестбенчи

Проверка производительности PLL и АЦП с помощью метрик для конкретных приложений.

Модели Mixed-Signal Blockset

Изучите подключаемую библиотеку с дополнительными моделями смешанных сигналов для АЦП, PLL, SerDes, SMPS.

Документация

Документация

Проектирование и симуляция аналоговых систем фазовой автоподстройки частоты (ФАПЧ)

Проектирование и симуляция аналоговых систем фазовой автоподстройки частоты (ФАПЧ) Проектирование и проверка PLL с использованием спецификации, включая фазовый шум (англ.)

Проектирование и проверка PLL с использованием спецификации, включая фазовый шум (англ.)

Simscape Electrical

Simscape Electrical