Filter Design HDL Coder

Основные возможности

- Генерация синтезируемого кода, полностью соответствующего стандартам IEEE 1076 VHDL и IEEE 1364-2001 Verilog

- Возможность контроля стратегии оптимизации кода и его стиля

- Возможность управления выбором аппаратных ресурсов, их количеством, а также контроль максимальной тактовой частоты работы фильтра

- Автоматическая генерация тестов для упрощения процедуры верификации и валидации сгенерированного кода

- Генерация скриптовых сценариев синтеза и симуляции

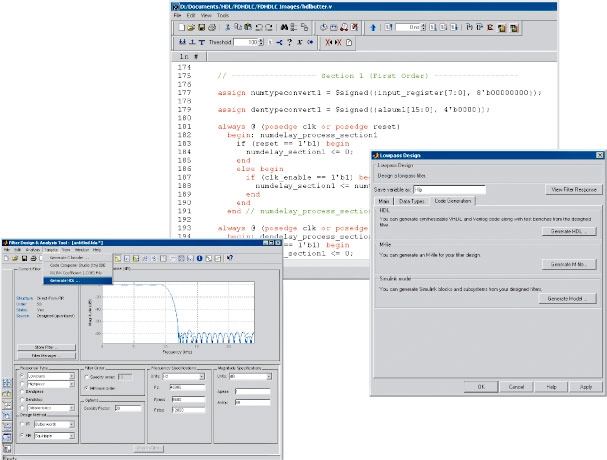

Сгенерированный HDL-код является читаемым и имеет корректный стиль форматирования, что позволяет разработчикам, в случае необходимости, проводить его анализ и изменять его. Автоматическая генерация тестовых сценариев позволяет ускорить верификацию проекта, а также корректность изменений, которые были внесены разработчиками в сгенерированный код.

Работа с Filter Design HDL coder

Filter Design HDL Coder является интегрированным инструментом DSP System Toolbox и вместе они формируют унифицированную среду разработки систем ЦОС. Вы можете генерировать код VHDL и Verilog и разрабатывать фильтры как при помощи консольных команд и языка MATLAB, так и из DSP System Toolbox, используя приложение Filter Designer или приложение Filter Builder.

Разработка фильтров с арифметикой в фиксированной точке

Входные данные для проектирования в Filter Design HDL Coder — это фильтр с квантованными коэффициентами, который вы можете создать одним из двух способов:

- Разработать фильтр и выполнить квантование коэффициентов в DSP System Toolbox;

- Разработать фильтр в Signal Processing Toolbox и выполнить квантование его коэффициентов при помощи DSP System Toolbox.

Filter Design HDL coder может принимать на вход следующие системные объекты, описывающие фильтры со следующими структурами:

Discrete-time finite impulse response (FIR), который может иметь симметричную, асимметричную или транспонированную структуру.

Second order section (SOS) infinite response (IIR), включая прямую форму I и II типа и транспонированную структуру.

Многоскоростные фильтры, в частности каскадно-гребенчатые интерполирующие и децимирующие фильтры Хогенауера (CIC), интерполирующие и децимирующие FIR фильтры прямой и транспонированной структуры.

Фильтры Фарроу.

Filter Design HDL coder может генерировать код для каскадных, многоскоростных и других цифровых фильтров. Каждая из приведенных структур цифровых фильтров поддерживает реализацию как в арифметике с фиксированной точкой, так и с плавающей. Кроме того, поддерживается генерация коэффициентов в беззнаковом формате для FIR фильтров в арифметике с фиксированной точкой.

Генерация HDL-кода для фильтров с фиксированной точкой

Filter Design HDL coder генерирует HDL-код, реализующий фильтр в фиксированной точке и тестовый сценарий. Вы можете изменять настройки синтеза с целью изменения и форматирования HDL-кода:

- Управлять именованием элементов фильтра;

- Указывать параметры портов ввода-вывода;

- Использовать продвинутые опции генерации кода.

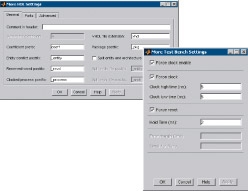

Все свойства имеют начальные значения (значения по умолчанию). Вы можете изменить результат генерации HDL-кода, изменяя данные настройки в Filter Builder app или Filter Design and Analysis app. Эти приложения позволят вам внести следующие изменения:

- Выбрать язык HDL;

- Управлять именами фалов и директорией генерации;

- Вернуть настройки к исходным значениям;

- Управлять параметрами оптимизации HDL-кода.

Тестирование и синтез сгенерированного HDL-кода

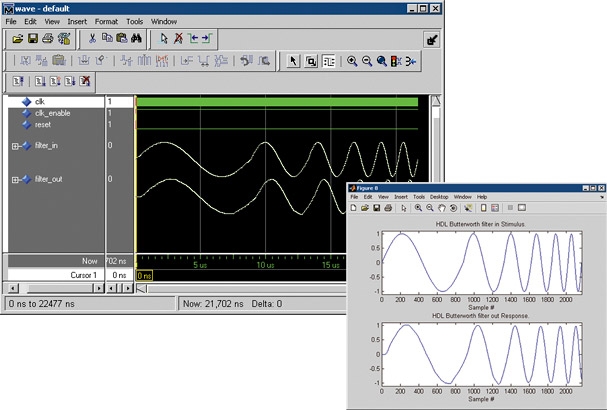

Вы можете сформировать Verilog и ли VDHL тестовый сценарий для симуляции и верификации сгенерированного HDL-кода. Кроме того, используя HDL Verifier, вы можете сгенерировать блок совместной симуляции HDL фильтра и Simulink модели при помощи интеграции в данную модель одного из наиболее распространенных HDL симуляторов (Cadence Incisive, Mentor Graphics ModelSim, or Mentor Graphics Questa HDL). Данный подход совместной симуляции позволяет упростить верификацию разработанной системы фильтрации путем сравнения работы поведенческой модели в Simulink и HDL-кода в симуляторе. Подобная интеграция расширяет возможности визуализации и анализа, распространяя широкие возможности MATLAB в этой сфере на HDL-код.

Оптимизация архитектуры

После процедуры квантования коэффициентов вы можете запустить Filter Design HDL-кодер и сконфигурировать параметры оптимизации, стиля кодирования или формат тестового сценария. Поддерживаются следующие возможности оптимизации:

- CSD-оптимизация коэффициентов фильтра для упрощения вычисления операции умножения и уменьшения занимаемых фильтром ресурсов при сохранении или увеличении тактовой частоты его работы

- Настройка баланса между количеством занимаемых ресурсов и тактовой частотой работы фильтра

- Выбор ресурсов реализации арифметических операций, хранения промежуточных значений и коэффициентов

Кроме того Filter Design HDL coder позволяет формировать сценарии синтеза для ускорения рабочего процесса.

Документация

Документация

Базовый КИХ-фильтр

Базовый КИХ-фильтр DSP System Toolbox

DSP System Toolbox