История успеха АО «РТИ»: оптимизация кода математического модуля на языке VHDL

АО «РТИ» оптимизировали модуль расчёта фаз в плавающей точке на языке VHDL.

«Специалисты ЦИТМ Экспонента доказали, что техника автоматической генерации кода для ПЛИС не только применима к нашим задачам, но и существенно модернизирует процесс разработки и отработки Изделия»,

– Андрей Климов, АО «РТИ».

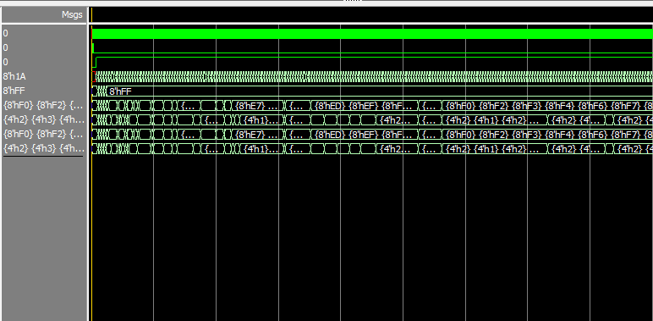

Результаты моделирования в Simulink и автоматической генерации VHDL-кода в арифметике с плавающей точкой:

- Оптимизация площади: код использует на 23% меньше логических элементов и на 90% меньше аппаратных умножителей в ПЛИС

- Оптимизация скорости: максимальная тактовая частота выше в 1.5 раза

- Время разработки: менее 1 месяца

Задача

Оптимизировать существующий модуль расчёта компенсации фаз для антенной решётки, реализованный на языке VHDL в арифметике с плавающей точкой.

Решение

Использовать Simulink и HDL Coder для создания модели математического модуля, автоматической генерации кода и верификации относительно тестовых данных

Результаты

- Время разработки менее 1 месяца.

- Оптимизированный код занимает на 23% меньше логических элементов и на 90% меньше DSP48E1.

- Максимальная частота повысилась более чем на 50%.

Таблица 1. Сравнение использования ресурсов ПЛИС

Скачать статью полностью можно по ссылке ниже.